|

АвтоАвтоматизацияАрхитектураАстрономияАудитБиологияБухгалтерияВоенное делоГенетикаГеографияГеологияГосударствоДомДругоеЖурналистика и СМИИзобретательствоИностранные языкиИнформатикаИскусствоИсторияКомпьютерыКулинарияКультураЛексикологияЛитератураЛогикаМаркетингМатематикаМашиностроениеМедицинаМенеджментМеталлы и СваркаМеханикаМузыкаНаселениеОбразованиеОхрана безопасности жизниОхрана ТрудаПедагогикаПолитикаПравоПриборостроениеПрограммированиеПроизводствоПромышленностьПсихологияРадиоРегилияСвязьСоциологияСпортСтандартизацияСтроительствоТехнологииТорговляТуризмФизикаФизиологияФилософияФинансыХимияХозяйствоЦеннообразованиеЧерчениеЭкологияЭконометрикаЭкономикаЭлектроникаЮриспунденкция

Синхронные 0-защелки

Триггеры

Для хранения информации в компьютере используются различные типы элементов памяти, они могут быть статическими, позволяющими хранить двоичную информацию сколь угодно долго, при наличии напряжения. Динамические элементы памяти применяются при построении оперативной памяти. Рассмотрим статические элементы памяти, которые используют процессор. Триггеры относятся к цифровым автоматам в отличии от комбинационных схем, состояние на выходе триггера в данный момент времени определяется не только состояниями на входах триггера в этот же момент, но и предыдущим состоянием триггера. Основу триггера составляет Би стабильная ячейка имеющая 2 устойчивых состояния. Существование двух устойчивых состояний Би стабильной ячейки объясняется наличием в её схеме обратных связей, позволяющих сигналу с выхода элемента поступать на его же вход через второй элемент.

Асинхронный SR триггер.

Два входа S (Setting — установками) R (Resetting — сброс) и два комплиментарных выхода Q и инверсия Q.

Варианты использования

- Хотим узнать состояние ячейки, посылаем на входы s и r.

- Хотим установить состояние триггера в 1(посылаем в s 1).

- Хотим сбросить состояние триггера в 0, посылаем в r единицу.

Синхронный SR триггер

Иногда необходимо, что бы триггер менял свое состояние только в определенные моменты.

Эта схема имеет дополнительный синхронизирующий вход, который по большей части равен 0. Если этот вход равен 0, то оба выхода элементов конъюнкции равны 0, и независимо от значений S и R триггер не меняет свое состояние. Когда значение синхронизирующего входа равно 1, действие элементов конъюнкции прекращается, и состояние триггера становится зависимым от S и R.

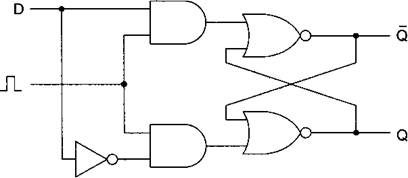

Синхронные 0-защелки

Неопределенность в триггере возникает в том случае, если S=R=1. Чтобы не дать её возникнуть используются D-триггеры.

Так как входной сигнал в нижний элемент конъюнкции всегда является обратным кодом входного сигнала в верхний элемент конъюнкции, ситуация, когда оба входа равны 1 никогда не возникнет. Когда D равен 1 и синхронизирующий вход равен 1 триггер переходит в состояние Q=1. Когда D равно 0 и синхронизирующий вход равен 1 триггер переходит в состояние Q=0.Сохраненное значение всегда доступно на выходе Q. Эта схема позволяет организовать память объемом 1 бит.

Для хранения 1 бита информации может быть использован триггер.

Поиск по сайту: