|

АвтоАвтоматизацияАрхитектураАстрономияАудитБиологияБухгалтерияВоенное делоГенетикаГеографияГеологияГосударствоДомДругоеЖурналистика и СМИИзобретательствоИностранные языкиИнформатикаИскусствоИсторияКомпьютерыКулинарияКультураЛексикологияЛитератураЛогикаМаркетингМатематикаМашиностроениеМедицинаМенеджментМеталлы и СваркаМеханикаМузыкаНаселениеОбразованиеОхрана безопасности жизниОхрана ТрудаПедагогикаПолитикаПравоПриборостроениеПрограммированиеПроизводствоПромышленностьПсихологияРадиоРегилияСвязьСоциологияСпортСтандартизацияСтроительствоТехнологииТорговляТуризмФизикаФизиологияФилософияФинансыХимияХозяйствоЦеннообразованиеЧерчениеЭкологияЭконометрикаЭкономикаЭлектроникаЮриспунденкция

Дельта-сигма преобразователь с уравновешиванием заряда

Данный тип интегрирующего преобразователя является наиболее простым при достаточной точности.

Он является преобразователем с заданным зарядом. В первом (очень кратковременном) такте в интегрирующий конденсатор вносится заданный электрический заряд. Во время второго - происходит компенсация этого заряда зарядом проинтегрированного входного тока преобразователя. Поскольку длительность первого такта мала то на выходе преобразователя измеряют длительность (или частоту) всего цикла.

АЦП последовательного приближения

Преобразователь этого типа, называемый в литературе также АЦП с поразрядным уравновешиванием, является наиболее распространенным вариантом последовательных АЦП.

В основе работы этого класса преобразователей лежит принцип дихотомии, т.е последовательного сравнения измеряемой величины с 1/2, 1/4, 1/8 и т.д. от возможного максимального значения ее. Это позволяет для N-разрядного АЦП последовательного приближения выполнить весь процесс преобразования за N последовательных шагов (итераций) вместо 2N-1 при использовании последовательного счета и получить существенный выигрыш в быстродействии. Так, уже при N=10 этот выигрыш достигает 100 раз и позволяет получить с помощью таких АЦП до 105...106 преобразований в секунду. В то же время статическая погрешность этого типа преобразователей, определяемая в основном используемым в нем ЦАП, может быть очень малой, что позволяет реализовать разрешающую способность до 18 двоичных разрядов при частоте выборок до 200 кГц (например, DSP101 фирмы Burr-Brown).

Рассмотрим принципы построения и работы АЦП последовательного приближения на примере классической структуры (рис. 9а) 4-разрядного преобразователя, состоящего из трех основных узлов: компаратора, регистра последовательного приближения (РПП) и ЦАП.

После подачи команды "Пуск" с приходом первого тактового импульса РПП принудительно задает на вход ЦАП код, равный половине его шкалы (для 4-разрядного ЦАП это 10002=810). Благодаря этому напряжение Uос на выходе ЦАП (рис. 9б)

Uос=23h.

где h - квант выходного напряжения ЦАП, соответствующий единице младшего разряда (ЕМР). Эта величина составляет половину возможного диапазона преобразуемых сигналов. Если входное напряжение больше, чем эта величина, то на выходе компаратора устанавливается 1, если меньше, то 0. В этом последнем случае схема управления должна переключить старший разряд d3 обратно в состояние нуля. Непосредственно вслед за этим остаток

Uвх - d3 23 h

таким же образом сравнивается с ближайшим младшим разрядом и т.д. После четырех подобных выравнивающих шагов в регистре последовательного приближения оказывается двоичное число, из которого после цифро-аналогового преобразования получается напряжение, соответствующее Uвх с точностью до 1 ЕМР. Выходное число может быть считано с РПП в виде параллельного двоичного кода по N линиям. Кроме того, в процессе преобразования на выходе компаратора, как это видно из рис. 9б, формируется выходное число в виде последовательного кода старшими разрядами вперед.

Быстродействие АЦП данного типа определяется суммой времени установления tуст ЦАП до установившегося значения с погрешностью, не превышающей 0,5 ЕМР, времени переключения компаратора tк и задержки распространения сигнала в регистре последовательного приближения tз. Сумма tк+ tз является величиной постоянной, а tуст уменьшается с уменьшением веса разряда. Следовательно для определения младших разрядов может быть использована более высокая тактовая частота. При поразрядной вариации fтакт возможно уменьшение времени преобразования tпр на 40%. Для этого в состав АЦП может быть включен контроллер.

При работе без устройства выборки-хранения апертурное время равно времени между началом и фактическим окончанием преобразования, которое так же, как и у АЦП последовательного счета, по сути зависит от входного сигнала, т.е. является переменным. Возникающие при этом апертурные погрешности носят также нелинейный характер. Поэтому для эффективного использования АЦП последовательного приближения, между его входом и источником преобразуемого сигнала следует включать УВХ. Большинство выпускаемых в настоящее время ИМС АЦП последовательного приближения (например, 12-разрядный МАХ191, 16-разрядный AD7882 и др.), имеет встроенные устройства выборки-хранения или, чаще, устройства слежения-хранения (track-hold), управляемые сигналом запуска АЦП. Устройство слежения-хранения отличается тем, что постоянно находится в режиме выборки, переходя в режим хранения только на время преобразования сигнала.

Данный класс АЦП занимает промежуточное положение по быстродействию, стоимости и разрешающей способности между последовательно-параллельными и интегрирующими АЦП и находит широкое применение в системах управления, контроля и цифровой обработки сигналов.

Рассмотрим принципы построения и работы АЦП последовательного приближения на примере классической структуры (рис. 9а) 4-разрядного преобразователя, состоящего из трех основных узлов: компаратора, регистра последовательного приближения (РПП) и ЦАП.

После подачи команды "Пуск" с приходом первого тактового импульса РПП принудительно задает на вход ЦАП код, равный половине его шкалы (для 4-разрядного ЦАП это 10002=810). Благодаря этому напряжение Uос на выходе ЦАП (рис. 9б)

Uос=23h.

где h - квант выходного напряжения ЦАП, соответствующий единице младшего разряда (ЕМР). Эта величина составляет половину возможного диапазона преобразуемых сигналов. Если входное напряжение больше, чем эта величина, то на выходе компаратора устанавливается 1, если меньше, то 0. В этом последнем случае схема управления должна переключить старший разряд d3 обратно в состояние нуля. Непосредственно вслед за этим остаток

Uвх - d3 23 h

таким же образом сравнивается с ближайшим младшим разрядом и т.д. После четырех подобных выравнивающих шагов в регистре последовательного приближения оказывается двоичное число, из которого после цифро-аналогового преобразования получается напряжение, соответствующее Uвх с точностью до 1 ЕМР. Выходное число может быть считано с РПП в виде параллельного двоичного кода по N линиям. Кроме того, в процессе преобразования на выходе компаратора, как это видно из рис. 9б, формируется выходное число в виде последовательного кода старшими разрядами вперед.

Быстродействие АЦП данного типа определяется суммой времени установления tуст ЦАП до установившегося значения с погрешностью, не превышающей 0,5 ЕМР, времени переключения компаратора tк и задержки распространения сигнала в регистре последовательного приближения tз. Сумма tк+ tз является величиной постоянной, а tуст уменьшается с уменьшением веса разряда. Следовательно для определения младших разрядов может быть использована более высокая тактовая частота. При поразрядной вариации fтакт возможно уменьшение времени преобразования tпр на 40%. Для этого в состав АЦП может быть включен контроллер.

При работе без устройства выборки-хранения апертурное время равно времени между началом и фактическим окончанием преобразования, которое так же, как и у АЦП последовательного счета, по сути зависит от входного сигнала, т.е. является переменным. Возникающие при этом апертурные погрешности носят также нелинейный характер. Поэтому для эффективного использования АЦП последовательного приближения, между его входом и источником преобразуемого сигнала следует включать УВХ. Большинство выпускаемых в настоящее время ИМС АЦП последовательного приближения (например, 12-разрядный МАХ191, 16-разрядный AD7882 и др.), имеет встроенные устройства выборки-хранения или, чаще, устройства слежения-хранения (track-hold), управляемые сигналом запуска АЦП. Устройство слежения-хранения отличается тем, что постоянно находится в режиме выборки, переходя в режим хранения только на время преобразования сигнала.

Данный класс АЦП занимает промежуточное положение по быстродействию, стоимости и разрешающей способности между последовательно-параллельными и интегрирующими АЦП и находит широкое применение в системах управления, контроля и цифровой обработки сигналов.

|

Параллельные аналого-цифровые преобразователи динамического типа относятся к области электрорадиотехники, связанной с цифровой обработкой аналоговых сигналов. Технический результат заключается в уменьшении аппаратурных затрат в параллельных статических АЦП путем осуществления динамического квантования опорных уровней, а также возможность регулирования диапазона изменения входного сигнала в параллельных АЦП с динамическим смещением входного сигнала. Для этого в вариантах аналого-цифровые преобразователи динамического типа основаны на одновременном сравнении напряжения входного сигнала с n опорными уровнями, формируемые динамическим квантованием; на одновременном сравнении динамически изменяющихся квантованных смещений напряжения входного сигнала с напряжением, равным половине напряжения опорного сигнала; использовании n-разрядной линейки источников двоично-взвешенных напряжений, из которой создаются уровни следящих опорных напряжений на параллельно включенных относительно входного сигнала компараторах. 5 н.п. ф-лы, 12 ил.

Изобретение относится к области электрорадиотехники, связанной с цифровой обработкой аналоговых сигналов.

При параллельном аналого-цифровом преобразовании [1] входное напряжение подается на одноименные входы группы компараторов и приводится к унитарному коду одновременным сравнением с N эквидистантными опорными напряжениями, подаваемыми на вторые входы компараторов. В зависимости от текущего значения входного напряжения на шкале уровней квантования определяется состояние выходов компараторов, которое преобразуется логической схемой в n-разрядный двоичный код. Отличительной особенностью данного способа является то, что набор уровней квантования, создаваемый обычно резистивным делителем, является статическим, а разрядность n выходного двоичного кода связана с количеством уровней квантования соотношением N=2n-1. Поскольку точность преобразования зависит от количества опорных уровней, разбивающих диапазон изменения входного напряжения, и, следовательно, от количества компараторов, то при обеспечении достаточного качества аппаратурные затраты преобразования велики.

Известен аналого-цифровой преобразователь [2], в котором входное напряжение непосредственно представляется на выходах инверторов в параллельном двоичном коде, а количество инверторов n равно разрядности двоичного кода. Инверторы осуществляют сравнение анализируемого напряжения с порогом срабатывания, равным половине напряжения питания. Анализируемое напряжение для некоторого выбранного инвертора формируется из входного напряжения с помощью матрицы двоично-взвешенных резисторов, входы которой подключаются к выходам соответствующих инверторов, имеющих разрядность выше разрядности выбранного компаратора. Эти напряжения, подаваемые на входы инверторов, являются динамически изменяющимися смещениями входного сигнала, зависящими от состояний цифровых выходов преобразователя. Количество квантованных смещений для всего диапазона изменения входного сигнала равно N=2n-1. Эти признаки позволяют отнести данное устройство к параллельным аналого-цифровым преобразователям, в которых осуществляется динамическое квантование входного сигнала. Недостатком этого устройства является привязка опорного напряжения к напряжению питания устройства, а также определенные требования к свойствам инверторов.

Целью изобретения является уменьшение аппаратурных затрат в параллельных статических АЦП путем осуществления динамического квантования опорных уровней, а также возможность регулирования диапазона изменения входного сигнала в параллельных АЦП с динамическим смещением входного сигнала.

Технический результат достигается тем, что в параллельный аналого-цифровой преобразователь, содержащий источник опорного напряжения и группу компараторов, количество которых n равно разрядности двоичного кода, представляющего преобразуемое аналоговое напряжение в цифровом виде, упорядоченных по порядку номеров разрядов двоичного кода так, что некоторый k-й компаратор создает k-й разряд выходного кода, первые одноименные входы компараторов соединены и на них подается напряжение входного сигнала, вводится группа цифроаналоговых преобразователей, количество которых равно количеству компараторов, опорные входы которых соединяются с источником опорного напряжения; выход первого цифроаналогового преобразователя подключается ко второму входу компаратора младшего разряда, а выход каждого последующего цифроаналогового преобразователя подключается ко второму входу компаратора вышеследующего разряда; количество входов цифроаналогового преобразователя, подключенного к компаратору с k-м порядковым номером, равно разности между количеством разрядов преобразователя и порядковым номером компаратора; цифровой вход старшего разряда цифроаналогового преобразователя с k-м порядковым номером соединяется с выходом компаратора старшего разряда, каждый последующий вход k-го цифроаналогового преобразователя соединяется с выходом последующего компаратора, а цифровые входы младших значащих разрядов цифроаналоговых преобразователей соединяются и на них подается значение логической единицы, цифроаналоговый преобразователь компаратора старшего разряда вырождается в делитель опорного напряжения с коэффициентом деления на два.

Технический результат достигается тем, что параллельный аналого-цифровой преобразователь динамического типа, содержащий источник опорного напряжения и группу компараторов, количество n которых равно разрядности двоичного кода, представляющего преобразуемое аналоговое напряжение в цифровом виде, упорядоченных по порядку номеров разрядов двоичного кода так, что некоторый k-й компаратор формирует k-й разряд выходного кода; одноименные входы компараторов соединены и на них подается напряжение входного сигнала, содержит резистивные матрицы, формирующие опорные напряжения компараторов, выходы которых подключены ко вторым входам компараторов; количество входов резистивной матрицы, подключенной к компаратору с k-м порядковым номером, равно разности между количеством разрядов преобразователя и порядковым номером компаратора; входы резистивных матриц упорядочиваются по возрастанию весовых коэффициентов деления входных напряжений; преобразователь содержит двухтактные электронные ключи, количество которых на единицу меньше количества компараторов, одноименные входы ключей подключаются к общей нулевой точке, вторые входы ключей подключаются к источнику опорного напряжения, цепь управления первого ключа подключается к выходу компаратора старшего разряда, а цепь управления каждого последующего ключа подключается к выходу компаратора последующего разряда; к выходу электронного ключа, управляемого компаратором старшего разряда, подключаются входы резистивных матриц старших весовых коэффициентов, к выходу каждого последующего электронного ключа, подключаются последующие входы каждой матрицы, в соответствии с уменьшением их весовых коэффициентов; входы матриц с наименьшими весовыми коэффициентами и вход резистивной матрицы компаратора старшего разряда, являющейся делителем на два опорного напряжения, подключаются к источнику опорного напряжения.

Технический результат достигается тем, что параллельный аналого-цифровой преобразователь динамического типа, содержащий источник опорного напряжения и группу компараторов, количество n которых равно разрядности двоичного кода, представляющего преобразуемое аналоговое напряжение в цифровом виде, упорядоченных по порядку номеров разрядов двоичного кода так, что некоторый k-й компаратор формирует k-й разряд выходного кода; одноименные входы компараторов соединены и на них подается напряжение входного сигнала, содержит группу двухтактных электронных ключей, количество которых на единицу меньше количества компараторов; первые одноименные входы ключей подключаются к общей нулевой точке; вторые входы ключей подключаются к источнику опорного напряжения, цепь управления первого ключа подключается к выходу компаратора старшего разряда, а цепь управления каждого последующего ключа подключается к выходу компаратора последующего разряда; к выходу каждого электронного ключа подключается первый вход управления группы источников токов управляемых напряжением, второй вход которой соединяется с общей нулевой точкой; количество источников токов в группе равно разрядности k-го компаратора, управляющего ключом данной группы источников, а их токи имеют одинаковое двоично-взвешенное значение, пропорциональное разряду k-го компаратора; второй вход компаратора старшего значащего разряда соединяется с выходом делителя на два опорного напряжения преобразователя; второй вход каждого последующего k-го компаратора образует узел суммирования токов, к которому подключаются первыми выводами по одному источнику тока из каждой группы управляемых напряжением источников токов, имеющих разряд выше разряда данного компаратора, суммирующий резистор, на котором выделяется опорное напряжение компаратора, и источник начального тока управляемый напряжением, взвешенное значение которого пропорционально разряду данного компаратора, вторые выводы которых соединяются с общей нулевой точкой.

Технический результат достигается тем, что параллельный аналого-цифровой преобразователь, включающий источник опорного напряжения и группу компараторов, количество которых равно разрядности n двоичного кода, представляющего преобразуемое аналоговое напряжение в цифровом виде, упорядоченных по порядку номеров разрядов двоичного кода так, что некоторый k-й компаратор формирует k-й разряд выходного кода, одноименные входы компараторов соединены и на них подается напряжение входного сигнала, содержит блок источников напряжений, количество которых в блоке равно количеству компараторов и на выходах которых из опорного напряжения формируется последовательность двоично-взвешенных напряжений, упорядоченная по порядку понижения разряда напряжения так, что каждое последующее напряжение меньше предыдущего в два раза, а напряжение старшего разряда рано половине опорного напряжения; содержит двухтактные электронные ключи, количество которых на единицу меньше количества компараторов; одноименные входы ключей подключаются к общей нулевой точке, вторые входы ключей подключаются к выходам блока источников напряжения так, что вход первого ключа подключается к выходу старшего разряда, а второй вход каждого последующего ключа к последующему выходу блока источников; цепь управления первого ключа подключается к выходу компаратора старшего разряда, а цепь управления каждого последующего ключа подключается к выходу компаратора последующего разряда; содержит группу сумматоров напряжений, количество которых на единицу меньше количества компараторов, выход первого сумматора подключается ко второму входу компаратора младшего разряда, а выход каждого последующего сумматора подключается ко второму входу компаратора вышеследующего разряда, количество входов сумматора, подключенного к компаратору с k-м порядковым номером, равно разности между количеством разрядов преобразователя и порядковым номером компаратора; первый вход сумматора с k-м порядковым номером соединяется с выходным контактом первого ключа, каждый последующий вход k-го сумматора соединяется с выходом последующего ключа, а последний вход k-го сумматора подключается к выходу блока источников напряжений с k-м порядковым номером; второй вход компаратора старшего разряда подключается к выходу старшего разряда блока источников напряжений.

Технический результат достигается тем, что аналого-цифровой преобразователь, содержащий группу компараторов, количество которых равно разрядности n двоичного кода, представляющего преобразуемое аналоговое напряжение в цифровом виде, упорядоченных по порядку номеров разрядов двоичного кода так, что некоторый k-й компаратор создает k-й разряд выходного кода; к первому входу компаратора старшего разряда подключен источник входного напряжения, а к первому входу каждого k-го компаратора подключен выход матрицы двоично-взвешенных резисторов, количество ветвей в которой для k-го компаратора равно разности между количеством разрядов преобразователя и порядковым номером компаратора; ветви каждой матрицы упорядочиваются по возрастанию сопротивлений резисторов так, что каждый последующий резистор в два раза больше предыдущего, к базовому резистору матрицы, имеющему наименьшее сопротивление, подключен источник входного сигнала, дополняется источником опорного напряжения и группой двухтактных электронных ключей, количество которых на единицу меньше количества компараторов, одноименные входы ключей подключаются к общей нулевой точке, вторые входы ключей подключаются к источнику опорного напряжения; к выходу каждого компаратора, кроме компаратора младшего значащего разряда, подключается цепь управления двухтактным электронным ключом, к выходу электронного ключа, управляемого компаратором старшего разряда, подключаются резисторы двоично-взвешенных цепей, сопротивления которых в два раза больше сопротивлений базовых резисторов этих цепей, к выходу каждого электронного ключа, управляемого компаратором последующего разряда, подключаются последующие резисторы каждой матрицы, в соответствии с увеличением их сопротивления, вторые входы компараторов соединяются и на них подается через делитель напряжение, равное половине опорного напряжения.

На фиг.1 представлена принципиальная электрическая схема параллельного аналого-цифрового преобразователя с динамическим квантованием и прямым двоичным кодом на выходе. Преобразователь содержит источник опорного напряжения 1, цифроаналоговые преобразователи (ЦАП) 2, 3, 4, 5, 6 и компараторы 7, 8, 9, 10, 11.

На фиг.2 представлена принципиальная электрическая схема параллельного аналого-цифрового преобразователя с динамическим квантованием и обратным двоичным кодом на выходе. Преобразователь содержит источник опорного напряжения 1, цифроаналоговые преобразователи (ЦАП) 2, 3, 4, 5, 6 и компараторы 7, 8, 9, 10, 11.

На фиг.3 приведена временная диаграмма движения уровней квантования на компараторах при треугольном входном напряжении для 4-разрядного параллельного АЦП с динамическим квантованием и прямым двоичным кодом на выходе.

На фиг.4 представлена принципиальная электрическая схема параллельного аналого-цифрового преобразователя динамического типа на резистивных матрицах и прямым двоичным кодом на выходе. Преобразователь содержит источник опорного напряжения 1, электронные двухпозиционные ключи 2, 3, 4, 5, резистивные матрицы 6, 7, 8, 9 10, компараторы 11, 12, 13, 14, 15.

На фиг.5 представлена принципиальная электрическая схема параллельного аналого-цифрового преобразователя динамического типа на резистивных матрицах и обратным двоичным кодом на выходе. Преобразователь содержит источник опорного напряжения 1, электронные двухпозиционные ключи 2, 3, 4, 5, резистивные матрицы 6, 7, 8, 9, 10, компараторы 11, 12, 13, 14, 15.

На фиг.6 представлена принципиальная электрическая схема параллельного аналого-цифрового преобразователя динамического типа на источниках тока и прямым двоичным кодом на выходе. Преобразователь содержит источник опорного напряжения 1, делитель напряжения 2, электронные двухпозиционные ключи 3, 4, 5, 6, коммутируемые источники тока управляемые напряжением 7, 8, 9, 10, источники начального тока управляемые напряжением 11, 12, 13, 14, суммирующие резисторы 15, 16, 17, 18 и компараторы 19, 20, 21, 22, 23.

На фиг.7 представлена принципиальная электрическая схема параллельного аналого-цифрового преобразователя динамического типа на источниках тока и обратным двоичным кодом на выходе. Преобразователь содержит источник опорного напряжения 1, делитель напряжения 2, электронные двухпозиционные ключи 3, 4, 5, 6, коммутируемые источники тока, управляемые напряжением 7, 8, 9, 10, источники начального тока, управляемые напряжением 11, 12, 13, 14, суммирующие резисторы 15, 16, 17, 18 и компараторы 19, 20, 21, 22, 23.

На фиг.8 представлена принципиальная электрическая схема параллельного аналого-цифрового преобразователя динамического типа с прямым двоичным кодом на выходе. Преобразователь содержит источник опорного напряжения 1, блок источников двоично-взвешенных напряжений 2, электронные двухпозиционные ключи 3, 4, 5, 6, сумматоры напряжений 7, 8, 9, 10, компараторы 11, 12, 13, 14, 15.

На фиг.9 представлена принципиальная электрическая схема параллельного аналого-цифрового преобразователя динамического типа с обратным двоичным кодом на выходе. Преобразователь содержит источник опорного напряжения 1, блок источников двоично-взвешенных напряжений 2, электронные двухпозиционные ключи 3, 4, 5, 6, сумматоры напряжений 7, 8, 9, 10, компараторы 11, 12, 13, 14, 15.

На фиг.10 представлена принципиальная электрическая схема параллельного аналого-цифрового преобразователя с динамическим смещением и обратным двоичным кодом на выходе. Преобразователь содержит источник опорного напряжения 1, делитель напряжения 2, электронные двухпозиционные ключи 3, 4, 5, 6, матрицы двоично-взвешенных резисторов 7, 8, 9, 10, компараторы 11, 12, 13, 14, 15.

На фиг.11 представлена принципиальная электрическая схема параллельного аналого-цифрового преобразователя с динамическим смещением и прямым двоичным кодом на выходе. Преобразователь содержит источник опорного напряжения 1, делитель напряжения 2, электронные двухпозиционные ключи 3, 4, 5, 6, матрицы двоично-взвешенных резисторов 7, 8, 9, 10, компараторы 11, 12, 13, 14, 15.

На фиг.12 приведена временная диаграмма движения смещений преобразуемого напряжения и значений цифровых выходов компараторов при пилообразном входном напряжении для параллельного 4-разрядного АЦП с динамическим квантованием и прямым двоичным кодом на выходе.

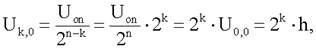

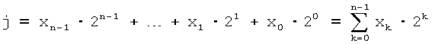

Принцип работы параллельных АЦП динамического типа с n-разрядным двоичным кодированием, представленных на чертежах фиг.1 и фиг.2, основан на одновременном сравнении напряжения входного сигнала с n опорными уровнями, формируемыми динамическим квантованием. Количество компараторов, составляющих параллельный АЦП динамического типа, равно разрядности выходного двоичного кода. Одноименные входы компараторов 7, 8, 9, 10, 11 объединяются и на них подается аналоговое преобразуемое напряжение Ux. Компараторы ранжируются по порядку номеров двоичного кода так, что каждый компаратор представляет определенный разряд двоичного кода. Напряжение опорного уровня для каждого компаратора создается привязанным к нему параллельным цифроаналоговым преобразователем 2, 3, 4, 5, 6 и подается на второй вход компаратора. Общее количество участков квантования, ограниченных опорными уровнями, при n-разрядном двоичном кодировании составляет величину N=2n-1. Для текущего значения преобразуемого входного напряжения создается текущая совокупность из n опорных уровней, обеспечивающая последовательное прохождение участков квантования в соответствии с законом изменения аналоговой переменной. В исходном состоянии устанавливается структура начальных опорных уровней. Напряжение начального опорного уровня для компаратора k-го разряда задается равным

где U0,0 - напряжение начального опорного уровня компаратора нулевого младшего значащего разряда (МЗР), задающее шаг квантования h=U0,0=ΔU преобразователя;

k=0, 1, …, n-1 - порядковый номер разряда двоичного кода и отражающего его компаратора.

Индекс напряжения Uk,j является двухсоставным. Первое число индекса обозначает порядковый номер компаратора, второе - порядковый номер участка квантования из множества N или порядковый номер опорного уровня, который является нижней границей рассматриваемого участка. Напряжение U(n-1),0 начального опорного уровня компаратора старшего значащего разряда (СЗР) равно половине опорного напряжения преобразователя. В процессе преобразования опорный уровень k-го компаратора зависит непосредственно от значения двоичного кода xn-1…xk…x1x0 на выходе АЦП, который представляет номер текущего участка квантования j в унитарной форме:

,

,

где xk=0 или 1 - логическое состояние выхода компаратора k-го разряда.

Для обеспечения квантованными опорными уровнями заданной траектории движения входной аналоговой переменной необходимо выполнение алгоритма формирования опорных уровней, заключающегося в том, что при прохождении аналоговой переменной опорного уровня (пробое опорного уровня) k-го компаратора и связанного с этим изменением его выхода, опорные уровни компараторов, имеющих разрядность ниже k, должны измениться на величину начального опорного напряжения k-го компаратора, или увеличиться, если состояние выхода приобретает высокий уровень, или уменьшиться, в противном случае. При расположении мгновенного значения входного напряжения Ux в j-м интервале распределение опорных уровней компараторов определяется из выражения:

Описанный алгоритм обеспечивает группа параллельных цифроаналоговых преобразователей таким образом, что любой j-й интервал, в котором находится входная переменная, всегда ограничен снизу и сверху опорными уровнями. Диапазон изменения входного сигнала задается источником опорного напряжения 1, которое подается на опорные входы цифроаналоговых преобразователей. Количество цифровых входов ЦАП, присоединенного к компаратору k-го разряда, равно разности между количеством разрядов и порядковым номером компаратора. На цифровые входы МЗР ЦАП подается значение логической единицы и этим обеспечивается установка начальных опорных уровней на компараторах. Цифроаналоговый преобразователь компаратора старшего разряда имеет один цифровой вход и вырождается в делитель опорного напряжения с коэффициентом деления на 2. АЦП фиг.1 выводит цифровое представление аналогового напряжения в прямом двоичном коде. Входной сигнал подается на не инвертирующие входы компараторов, а опорные уровни на инвертирующие. Обратный двоичный код формирует АЦП фиг.2, в котором входное напряжение подается на инвертирующие входы, а напряжения опорных уровней на не инвертирующие. В этом случае логические входы цифро-аналоговых преобразователей являются инверсными.

На фиг.3 приведена временная диаграмма движения опорных уровней и значений цифровых выходов компараторов для 4-разрядного параллельного АЦП с динамическим квантованием при пилообразном линейно-изменяющемся входном напряжении.

Параллельные аналого-цифровые преобразователи динамического типа с прямым кодом на выходе (фиг.4) и обратным кодом на выходе (фиг.5) работают по тому же принципу, что и устройства, представленные на фиг.1 и фиг.2. Количество компараторов АЦП равно разрядности выходного двоичного кода. Одноименные входы компараторов 11, 12, 13, 14, 15 объединяются и на них подается аналоговое преобразуемое напряжение Ux. Компараторы ранжируются по порядку номеров двоичного кода так, что каждый компаратор представляет определенный разряд двоичного кода. Напряжение опорного уровня для каждого компаратора создается привязанной к нему резистивной матрицей 6, 7, 8, 9, 10 и подается на второй вход компаратора. Резистивные матрицы RM представляют собой известные компоненты цифроаналоговых преобразователей, которые строятся в инверсном включении или на цепях двоично-взвешенных резисторов, или делителях постоянного импеданса типа R-2R. Количество разрядных входов матрицы, присоединенной к компаратору k-го разряда, равно (n-k). Входы МЗР матриц непосредственно подключаются к источнику опорного напряжения 1, этим обеспечивается установка начальных опорных уровней компараторов. Матрица компаратора старшего разряда имеет один вход и вырождается в делитель опорного напряжения с коэффициентом деления на 2. Коммутации входов матриц осуществляются общими последовательно-параллельными электронными ключами 2, 3, 4, 5, обеспечивающими подключение своих выходов либо к источнику опорного напряжения 1, либо к общей нулевой точке. Цепь управления каждого ключа соединяется с выходом компаратора определенного разряда, значение которого выше младшего значащего разряда. Соответственно этим соединениям выходы ключей образуют шины разрядов 1, …, k, …, n-1, к которым подключаются входы резистивных матриц соответствующих разрядов. АЦП фиг.4 создает на выходе число в прямом двоичном коде. Входной сигнал подается на неинвертирующие входы компараторов, а опорные уровни на инвертирующие. Обратный двоичный код формирует АЦП на фиг.5, в котором входное напряжение подается на инвертирующие входы, напряжения опорных уровней на неинвертирующие, а управление электронными ключами осуществляется в инверсном режиме. Такая конфигурация устройств позволяет уменьшить количество коммутирующих элементов по сравнению с устройствами на фиг.1 и фиг.2 в том случае, если цифроаналоговые преобразователи последних исполняются на тех же резистивных матрицах.

Аналого-цифровые преобразователи динамического типа представляют цифровой эквивалент входного напряжения прямым двоичным кодом (фиг.6) или обратным двоичным кодом (фиг.7). АЦП работают по тому же принципу, что и устройства, представленные на фиг.1 и фиг.2. Рассматриваемые параллельные динамические АЦП используют общие переключатели токов для входящих в их состав поразрядных ЦАП на источниках тока (ИТ). Количество компараторов АЦП равно разрядности выходного двоичного кода. Одноименные входы компараторов 19, 20, 21, 22, 23 объединяются и на них подается аналоговое входное напряжение Ux. Уровни опорных напряжений подаются на вторые входы компараторов. Опорный уровень Un-1=Uоп/2 компаратора старшего разряда 19 подается через делитель напряжения 2 от опорного источника 1. Опорные уровни U0, …, Uk, …, Un-2 на вторых входах остальных компараторов формируются как падение напряжения на суммирующих резисторах 15, 16, 17, 18 при протекании токов от источников токов управляемых напряжением (ИТУН) Uоп, разбитых на две группы. Источники тока 7, 8, 9, 10 представляют группу коммутируемых источников, а источники начальных токов 11, 12, 13, 14 - группу постоянных источников тока, обеспечивающих уровни начальных опорных напряжений на компараторах. Источники каждой группы привязаны к определенным компараторам. Привязка ИТ коммутируемой группы к компаратору осуществляется по цепи управления ключа, коммутирующего напряжение на входе ИТУН. Источники начального тока непосредственно подключаются к одному из входов компаратора, который и задает их порядковый номер. Коэффициент передачи k-го ИТУН из динамической группы обозначим как gkd, а из статической группы - gkc. Коэффициентами передачи источников токов управляемых напряжением, величины которых зависят от разряда источника тока, обеспечивают двоично-взвешенные токи источников:

Ток, протекающий через суммирующее сопротивление k-го компаратора, равен:

Формула отражает тот факт, что через суммирующее сопротивление k-го компаратора протекают токи ИТУН динамической группы, управляемые цифрами xm выходного кода, разряд которых m больше k. Уровень опорного напряжения на входе k-го компаратора, следовательно, равен:

При выполнении условия g0·R=1, распределение опорных уровней на компараторах совпадает с распределением в устройствах на фиг.1 и фиг.2, рассчитываемым по формуле (1). АЦП на фиг.6 формирует на выходе число в прямом двоичном коде. Входной сигнал подается на неинвертирующие входы компараторов, а опорные уровни на инвертирующие. Обратный двоичный код создает АЦП на фиг.7, в котором входное напряжение подается на инвертирующие входы, напряжения опорных уровней - на неинвертирующие, управление электронными ключами осуществляется в инверсном режиме.

В аналого-цифровых преобразователях динамического типа на фиг.8 и фиг.9 используется n-разрядная линейка источников двоично-взвешенных напряжений, из которой создаются уровни следящих опорных напряжений на параллельно включенных относительно входного сигнала компараторах. Количество компараторов в АЦП равно разрядности выходного двоичного кода. Одноименные входы компараторов 11, 12, 13, 14, 15 объединяются и на них подается аналоговое входное напряжение Ux. Напряжение опорного уровня для каждого компаратора создается привязанным к нему сумматором напряжений 7, 8, 9, 10 и подается на второй вход компаратора. Сумматоры формируют опорные напряжения компараторов сложением напряжений от блока источников двоично-взвешенных напряжений 2, который является n-ступенчатым делителем опорного напряжения Uon устройства. Напряжение на произвольном k-м выходе блока источников 2 составляет величину

где k принимает значения из ряда 0, 1, …, n-1. Количество входов сумматора произвольного k-го разряда равно разности между количеством разрядов n и порядковым номером сумматора k. На один из равнозначных входов сумматора k-го разряда подается напряжение с k-го выхода блока источников 2, обеспечивающее начальное опорное напряжение k-го компаратора. Остальные входы этого сумматора подключаются через коммутирующие двухпозиционные ключи или к выходам блока источников, разряды которых больше k, или к общей нулевой точке, в зависимости от логических состояний выходов компараторов. Величина опорного напряжения на входе k-го компаратора равна:

На опорный вход компаратора старшего значащего разряда непосредственно подается напряжение, равное половине напряжения опорного источника 1. АЦП на фиг.8 формирует на выходе число в прямом двоичном коде. Входной сигнал подается на неинвертирующие входы компараторов, а опорные уровни на инвертирующие. Обратный двоичный код создает АЦП на фиг.9, в котором входное напряжение подается на инвертирующие входы, напряжения опорных уровней на неинвертирующие, а управление электронными ключами осуществляется в инверсном режиме.

Принцип работы параллельных АЦП динамического типа с n-разрядным двоичным кодированием, представленных на фиг.10 и фиг.11, основан на одновременном сравнении динамически изменяющихся квантованных смещений напряжения входного сигнала с напряжением, равным половине напряжения опорного источника. Количество компараторов, составляющих параллельный АЦП динамического типа, равно разрядности выходного двоичного кода. Одноименные входы компараторов 11, 12, 13, 14, 15 объединяются и на них подается напряжение через делитель напряжения 2 от источника опорного напряжения 1. Компараторы ранжируются по порядку номеров двоичного кода так, что каждый компаратор представляет определенный разряд двоичного кода. Анализируемые напряжения, являющиеся смещениями входного сигнала Ux, формируются матрицами двоично-взвешенных резисторов 7, 8, 9, 10 и подаются на вторые сигнальные входы компараторов. Количество цифровых входов матрицы k-го разряда равно разности между порядковым номером СЗР (n-1) и порядковым номером матрицы k. Общее количество квантованных смещений входного сигнала во всем диапазоне его изменения при n-разрядном двоичном кодировании составляет величину N=2n-1. Для текущего значения преобразуемого входного напряжения на сигнальных входах компараторов составляется текущая совокупность из n анализируемых напряжений, которые являются линейными преобразованиями входного напряжения на матрицах двоично-взвешенных резисторов. Структуры матриц, т.е. соединение их резисторов с полюсами источника опорного напряжения, задаются в текущий момент двоичным числом на выходе преобразователя. Смещение входного напряжения на входе компаратора k-го разряда осуществляется теми разрядами выходного кода, значение которых больше разряда k. Величина анализируемого напряжения на сигнальном входе k-го компаратора определяется из выражения:

,

,

где Ux - входное напряжение; Uon - напряжение опорного источника;

xi - двоичная цифра i-го разряда числа, управляющего матрицей k-го компаратора;

Xk - унитарная (десятичная) форма числа, управляющего матрицей k-го компаратора;

i - индекс перечисления разрядов, подключенных к цифровым входам (ключам) матриц k-го компаратора.

АЦП на фиг.10 создает цифровое представление аналогового напряжения в обратном двоичном коде. Модифицированные напряжения входного сигнала подаются на инвертирующие входы компараторов, а уровень опорного напряжения - на неинвертирующие. Прямой двоичный код формирует АЦП на фиг.11, в котором уровни входных напряжений подаются на неинвертирующие входы, а напряжения опорного уровня - на инвертирующие. В этом случае управление электронными ключами осуществляется в инверсном режиме.

На фиг.12 приведены временные диаграммы напряжений на входах и значений цифровых выходов компараторов для 4-разрядного параллельного АЦП с динамическими смещениями входного сигнала при треугольном линейно-изменяющемся входном напряжении.

ЛИТЕРАТУРА

1. У.Титце, К.Шенк. Полупроводниковая схемотехника. М.: Мир, 1983.

2. Prinn А.Е. Simple a-to-d converter. // Wireless World - may 1981, vol 87, No 1544, p.60.

1. Параллельный аналого-цифровой преобразователь динамического типа, содержащий источник опорного напряжения и группу компараторов, количество n которых равно разрядности двоичного кода, представляющего преобразуемое аналоговое напряжение в цифровом виде, упорядоченных по порядку номеров разрядов двоичного кода так, что некоторый k-й компаратор формирует k-й разряд выходного кода, первые одноименные входы компараторов соединены и на них подается напряжение входного сигнала, отличающийся тем, что устройство содержит группу цифроаналоговых преобразователей, количество которых равно количеству компараторов, опорные входы которых соединяются с источником опорного напряжения; выход первого цифроаналогового преобразователя подключается ко второму входу компаратора младшего разряда, а выход каждого последующего цифроаналогового преобразователя подключается ко второму входу компаратора вышеследующего разряда; количество входов цифроаналогового преобразователя, подключенного к компаратору с k-м порядковым номером, равно разности между количеством разрядов преобразователя и порядковым номером компаратора; цифровой вход старшего разряда цифроаналогового преобразователя с k-м порядковым номером соединяется с выходом компаратора старшего разряда, каждый последующий вход k-го цифроаналогового преобразователя соединяется с выходом последующего компаратора, а цифровые входы младших значащих разрядов цифроаналоговых преобразователей соединяются и на них подается значение логической единицы, цифроаналоговый преобразователь компаратора старшего разряда является делителем на два опорного напряжения.

2. Параллельный аналого-цифровой преобразователь динамического типа, содержащий источник опорного напряжения и группу компараторов, количество n которых равно разрядности двоичного кода, представляющего преобразуемое аналоговое напряжение в цифровом виде, упорядоченных по порядку номеров разрядов двоичного кода так, что некоторый k-й компаратор формирует k-й разряд выходного кода; одноименные входы компараторов соединены и на них подается напряжение входного сигнала, отличающийся тем, что ко вторым входам компараторов подключены выходы резистивных матриц, которые формируют опорные напряжения компараторов; количество входов резистивной матрицы, подключенной к компаратору с k-м порядковым номером, равно разности между количеством разрядов преобразователя и порядковым номером компаратора; входы резистивных матриц упорядочиваются по возрастанию весовых коэффициентов деления входных напряжений; преобразователь содержит двухтактные электронные ключи, количество которых на единицу меньше количества компараторов, одноименные входы ключей подключаются к общей нулевой точке, вторые входы ключей подключаются к источнику опорного напряжения, цепь управления первого ключа подключается к выходу компаратора старшего разряда, а цепь управления каждого последующего ключа подключается к выходу компаратора последующего разряда; к выходу электронного ключа, управляемого компаратором старшего разряда, подключаются входы резистивных матриц старших весовых коэффициентов, к выходу каждого последующего электронного ключа подключаются последующие входы каждой матрицы в соответствии с уменьшением их весовых коэффициентов; входы матриц с наименьшими весовыми коэффициентами и вход резистивной матрицы компаратора старшего разряда, являющейся делителем на два опорного напряжения, подключаются к источнику опорного напряжения.

3. Параллельный аналого-цифровой преобразователь динамического типа, содержащий источник опорного напряжения и группу компараторов, количество n которых равно разрядности двоичного кода, представляющего преобразуемое аналоговое напряжение в цифровом виде, упорядоченных по порядку номеров разрядов двоичного кода так, что некоторый k-й компаратор формирует k-й разряд выходного кода; одноименные входы компараторов соединены и на них подается напряжение входного сигнала, отличающийся тем, что преобразователь содержит группу двухтактных электронных ключей, количество которых на единицу меньше количества компараторов; первые одноименные входы ключей подключаются к общей нулевой точке; вторые входы ключей подключаются к источнику опорного напряжения, цепь управления первого ключа подключается к выходу компаратора старшего разряда, а цепь управления каждого последующего ключа подключается к выходу компаратора последующего разряда; к выходу каждого электронного ключа подключается первый вход управления группы источников токов управляемых напряжением, второй вход которой соединяется с общей нулевой точкой; количество источников токов в группе равно разрядности k-го компаратора, управляющего ключом данной группы источников, а их токи имеют одинаковое двоично-взвешенное значение, пропорциональное разряду k-го компаратора; второй вход компаратора старшего значащего разряда соединяется с выходом делителя на два напряжения, вход которого подключается к источнику опорного напряжения; второй вход каждого последующего k-го компаратора образует узел суммирования токов, к которому подключаются первыми выводами по одному источнику тока из каждой группы управляемых напряжением источников токов, имеющих разряд выше разряда данного компаратора, суммирующий резистор, на котором выделяется опорное напряжение компаратора, и источник начального тока, взвешенное значение которого пропорционально разряду данного компаратора, вторые выводы которых соединяются с общей нулевой точкой.

4. Параллельный аналого-цифровой преобразователь динамического типа, содержащий источник опорного напряжения и группу компараторов, количество n которых равно разрядности двоичного кода, представляющего преобразуемое аналоговое напряжение в цифровом виде, упорядоченных по порядку номеров разрядов двоичного кода так, что некоторый k-й компаратор формирует k-й разряд выходного кода; одноименные входы компараторов соединены и на них подается напряжение входного сигнала, отличающийся тем, что преобразователь содержит блок источников напряжений, количество которых в блоке равно количеству компараторов и на выходах которых из опорного напряжения формируется последовательность двоично-взвешенных напряжений, упорядоченная по порядку понижения разряда напряжения так, что каждое последующее напряжение меньше предыдущего в два раза, а напряжение старшего разряда рано половине опорного напряжения; содержит двухтактные электронные ключи, количество которых на единицу меньше количества компараторов; одноименные входы ключей подключаются к общей нулевой точке, вторые входы ключей подключаются к выходам блока источников напряжения так, что первый ключ подключается к выходу старшего разряда, а второй вход каждого последующего ключа к последующему выходу блока источников; цепь управления первого ключа подключается к выходу компаратора старшего разряда, а цепь управления каждого последующего ключа подключается к выходу компаратора последующего разряда; содержит группу сумматоров напряжений, количество которых на единицу меньше количества компараторов, выход первого сумматора подключается ко второму входу компаратора младшего разряда, а выход каждого последующего сумматора подключается ко второму входу компаратора вышеследующего разряда, количество входов сумматора, подключенного к компаратору с k-м порядковым номером, равно разности между количеством разрядов преобразователя и порядковым номером компаратора; первый вход сумматора с k-м порядковым номером соединяется с выходным контактом первого ключа, каждый последующий вход k-го сумматора соединяется с выходом последующего ключа, а последний вход k-го сумматора подключается к выходу блока источников напряжений с k-м порядковым номером; второй вход компаратора старшего разряда подключается к выходу старшего разряда блока источников напряжений.

5. Параллельный аналого-цифровой преобразователь динамического типа, содержащий группу компараторов, количество n которых равно разрядности двоичного кода, представляющего преобразуемое аналоговое напряжение в цифровом виде, упорядоченных по порядку номеров разрядов двоичного кода так, что некоторый k-й компаратор формирует k-й разряд выходного кода; к первому входу компаратора старшего разряда подключен источник входного напряжения, а к первому входу каждого k-го компаратора подключен выход матрицы двоично-взвешенных резисторов, количество ветвей в которой для k-го компаратора равно разности между количеством разрядов преобразователя и порядковым номером компаратора; ветви каждой матрицы упорядочиваются по возрастанию сопротивлений резисторов так, что каждый последующий резистор в два раза больше предыдущего, к базовому резистору матрицы, имеющему наименьшее сопротивление, подключен источник входного сигнала, отличающийся тем, что преобразователь содержит источник опорного напряжения и группу двухтактных электронных ключей, количество которых на единицу меньше количества компараторов, одноименные входы ключей подключаются к общей нулевой точке, вторые входы ключей подключаются к источнику опорного напряжения; к выходу каждого компаратора, кроме компаратора младшего значащего разряда, подключается цепь управления двухтактным электронным ключом, к выходу электронного ключа, управляемого компаратором старшего разряда, подключаются резисторы двоично-взвешенных цепей, сопротивления которых в два раза больше сопротивлений базовых резисторов этих цепей, к выходу каждого электронного ключа, управляемого компаратором последующего разряда, подключаются последующие резисторы каждой матрицы в соответствии с увеличением их сопротивления, вторые входы компараторов соединяются и на них подается через делитель напряжение, равное половине опорного напряжения.

Поиск по сайту: