|

АвтоАвтоматизацияАрхитектураАстрономияАудитБиологияБухгалтерияВоенное делоГенетикаГеографияГеологияГосударствоДомДругоеЖурналистика и СМИИзобретательствоИностранные языкиИнформатикаИскусствоИсторияКомпьютерыКулинарияКультураЛексикологияЛитератураЛогикаМаркетингМатематикаМашиностроениеМедицинаМенеджментМеталлы и СваркаМеханикаМузыкаНаселениеОбразованиеОхрана безопасности жизниОхрана ТрудаПедагогикаПолитикаПравоПриборостроениеПрограммированиеПроизводствоПромышленностьПсихологияРадиоРегилияСвязьСоциологияСпортСтандартизацияСтроительствоТехнологииТорговляТуризмФизикаФизиологияФилософияФинансыХимияХозяйствоЦеннообразованиеЧерчениеЭкологияЭконометрикаЭкономикаЭлектроникаЮриспунденкция

Триггеры

|

Читайте также: |

Триггеры – это большой класс электронных устройств, обладающих способностью длительно находиться в одном из двух устойчивых состояний и чередовать их под воздействием внешних условий.

В отличие от комбинационных логических схем, триггеры представляют собой логические устройства с памятью. Их выходные сигналы зависят не только от сигналов, приложенным к входам в данный момент времени, но и от сигналов, воздействовавших на них ранее.

В интегральной микросхематехнике триггеры выполняют либо на основе логических интегральных элементов (интегральные триггеры), либо как завершенный функциональный элемент – в виде микросхем.

По функциональному признаку различают триггеры типов RS, D, T, JK и др. Название триггера отражает особенности его управления и характеризует вид логического управления.

RS- триггер

RS- триггер имеет два информационных входа: R и S.

В нем возможны два устойчивых состояния.

§ при S =1 и R =0 триггер принимает состояние логической «1»;

§ при R=0, S=0 – состояние «0» (Q =0).

Иногда вход S называют единичным, а R – нулевым. Для триггера R-S- типа комбинация S =1; R =1 является запрещенной, так как после этой комбинации состояние триггера будет неопределенным (Х) и он может оказаться или в нуле, или в единице. Поэтому необходимо предусмотреть исключение этой комбинации.

| Вход | Выход

| Выход

| |||

| R | S | Q |

| Q |

|

| не определено | без изменений | ||||

| без изменений | не определено |

;

;

.

.

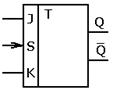

JK- триггер

В таблице состояний JK- триггера устранена строка неопределенности.

| Вход | Выход | |

| J | K |

|

|

| без изменений | |||

| переброс |

J и K - это виды установки выхода триггера Q- состояния 1 или 0.

В отличие от RS- триггера J = K =1 приводит к перебросу состояния выхода Q. JK- триггеры синхронизируются только перепадом потенциалов на входе S.

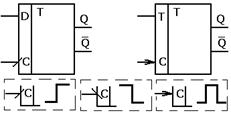

D- триггер

В D- триггере, или триггере задержки, при поступлении синхросигнала на вход С устанавливается состояние, соответствующее потенциалу на входе D.

T- триггер

В T - триггере, или в счетном триггере, изменение состояния происходит по фронту импульса на входе С. Сигнал на входе Т разрешает или запрещает срабатывание триггера.

Триггер Шмидта.

Логические элементы со свойствами триггера Шмидта имеют внутреннюю положительную обратную связь, глубина которой подобрана так, чтобы получить передаточную характеристику со значительным гистерезисом. Выходной сигнал логического элемента Шмидта имеет крутые импульсные перепады, длительность которых не зависит от скорости нарастания или спада входного сигнала.

Обычно применяются в схемах аппаратного устранения “дребезга” контактов.

Логические устройства

Логические устройства разделяют на два класса: комбинационные и последовательностные.

Устройство называют комбинационным, если его выходные сигналы в некоторый момент времени однозначно определяются входными сигналами, имеющими место в этот момент времени.

Иначе устройство называют последовательностным, или конечным автоматом(цифровым автоматом, автоматом с памятью).

Счетчики. Счетчик импульсов - это последовательностное цифровое устройство, обеспечивающее хранение слова информации и выполнение над ним микрооперации счета, заключающейся в изменении значения числа в счетчике на 1.

Счетчик представляет собой совокупность соединенных определенным образом триггеров.

Основной параметр счетчика – модуль счета. Это максимальное число единичных сигналов, которое может быть сосчитано счетчиком.

Счетчики классифицируют:

по модулю счета:

- двоичные,

- двоично-десятичные,

- с произвольным постоянным модулем счета,

- с переменным модулем счета.

по направлению счета:

-суммирующие,

-вычитающие,

-реверсивные.

по способу формирования внутренних связей:

-с последовательным переносом,

-с параллельным переносом,

-с комбинированным переносом,

-кольцевые.

Счетчиком называют цифровое устройство, предназначенное для подсчета числа импульсов. В процессе работы счетчик последовательно изменяет свое состояние в определенном порядке.

Длина списка разрешенных состояний счетчика называется модулем счета К С. Одно из возможных состояний счетчика принимается за начальное. Если счетчик начинал счет от начального состояния, то каждый импульс, кратный модулю счета Кс, снова устанавливает счетчик в начальное состояние, а на выходе счетчика появляется сигнал переноса Р(или займа Z).

Последовательность внутренних состояний счетчика можно кодировать различными способами. Чаще всего используют двоичное (двоичные счетчики) или двоично-десятичные (декадные счетчики) кодирование. Кроме этого находят применение счетчики с одинарным кодированием, когда состояние счетчика представлено местом расположения одной-единственной единицы или одного-единственного нуля (кольцевые счетчики), и унитарное кодирование, когда состояние счетчика представлено числом единиц или нулей (счетчики Джонсона).

Если коды расположены в возрасающем порядке, то счетчик называют суммирующим (Up-counter). Счетчики, у которых коды расположены в убывающем порядке, называют вычитающими (Down-counter), а счетчики, у которых направление перебора кода может изменяться, называют реверсивными (Up/Down-counter).

Если для работы счетчика требуется наличие синхросигнала, то такой счетчик называют синхронным. Счетчики, которые работают без синхросигналов, называют aсинхронными.

Счетчик СТ(обобщенная схема представлена на рис.) можно представить в общем случае как устройство, которое содержит входную логику, управляющую работой счетчика, и выходную логику, которая используется для указания окончания счета или формирования сигнала переноса Р или займа Z. Для приведения счетчика в начальное состояние используется сигнал сброса, поступающий на вход R.

Параллельный код для предварительной установки счетчика поступает на входы S0 … Sn. Сигнал разрешения параллельной загрузки М останавливает счет и позволяет подготовленным на входах S0 … Sn данным загрузиться в счетчик в момент прихода очередного тактового импульса С. Счетчик считает тактовые импульсы, поступающие на вход С, если присутствует сигнал разрешения счета на входе V.

Асинхронные счетчики. Асинхронный суммирующий счетчик можно выполнить на счетных триггерах любого типа.

Для приведения счетчика в начальное состояние используется сигнал сброса R, поступающий одновременно на все входы R-триггеров.

При построении асинхронного вычитающего счетчика достаточно заменить выходы  триггеров на прямые выходы Q. В этом случае при поступлении индекса сброса R на всех выходах счетчика установятся единичные уровни, а при поступлении счетных импульсов на вход С1 триггеры счетчика будут изменять свои состояния, описываемые последовательно убывающими двоичными числами.

триггеров на прямые выходы Q. В этом случае при поступлении индекса сброса R на всех выходах счетчика установятся единичные уровни, а при поступлении счетных импульсов на вход С1 триггеры счетчика будут изменять свои состояния, описываемые последовательно убывающими двоичными числами.

В асинхронном счетчике с приходом каждого последующего импульса на вход С1 переключаются сразу несколько триггеров. Однако переключение этих триггеров происходит не одновременно, а с некоторой задержкой относительно друг друга. При большом числе разрядов счетчика задержка выходного сигнала может быть значительной и сравнимой с периодом поступления счетных импульсов на С1. Максимальную частоту имеет первый триггер, а частоты переключения каждого последующего триггера вдвое меньше.

Синхронные счетчики. Для построения синхронных счетчиков используют различные типы счетных синхронных триггеров. Схемы одноразрядных синхронных счетчиков приведены на рисунке:

Переключение триггера происходит по положительному перепаду сигнала на входе С и при наличии сигнала разрешения на входе V. При этом на выходе триггера Q и выходе переноса Р устанавливаются уровни логической единицы. При отрицательном перепаде сигнала на входе С состояние триггера не изменяется. Очередное переключение триггера произойдет только по новому положительному перепаду импульса на входе С, при наличии сигнала разрешения на входе V. Таким образом, счетная ячейка обеспечивает синхронное деление на две частоты входных импульсов.

Двоичная вычитающая ячейка отличается от суммирующей тем, что прямой выход Q заменен на инверсный выход  . На выходе такой ячейки формируется сигнал займа Z = V*

. На выходе такой ячейки формируется сигнал займа Z = V*  .

.

Регистры сдвига. Триггерным регистром сдвига называют совокупность триггеров с определенными связями между ними, при которых они действуют как единое устройство. В регистрах сдвига организация этих связей такова, что при подаче тактового импульса, общего для всех триггеров, выходное состояние каждого триггера сдвигается в соседний. В зависимости от организации связей этот сдвиг может происходить влево или вправо:

Q2 →Q1,Q3 →Q2,Q4 →Q3, …, Qn →Qn-1 - сдвиг влево,

Q1 →Q2,Q2 →Q3,Q3 →Q4, …, Qn-1 →Qn - сдвиг вправо.

Ввод информации в регистр может выполняться различными способами, однако наиболее часто используют параллельный или последовательный ввод, при которых ввод двоичного числа осуществляется или одновременно во все разряды регистра, или последовательно во времени по отдельным разрядам.

Кольцевые счетчики. Разновидностью параллельных счетчиков являются кольцевые счетчики, выполненные на базе регистров сдвига. Простейшая схема кольцевого счетчика получается при замыкании прямого выхода регистра сдвига с его входом. В таком счетчике единица, записанная в регистр на первом такте, с выхода Qn снова попадает на его вход и далее весь цикл повторяется.

Основным недостатком кольцевых счетчиков является их низкая помехозащищенность. Например, если под действием помехи исчезнет записанная в счетчик единица, то все триггеры окажутся в нулевом состоянии и счетчик работать не может. Для устранения подобных сбоев используются различные способы коррекции состояния счетчика.

Счетчики Джонсона. Разновидностью кольцевых счетчиков являются счетчики Джонсона. В этих счетчиках вход регистра соединен не с выходом Q, а с инверсным выходом  . В результате, когда на вход счетчика поступают тактовые импульсы, то в начале все разряды счетчика заполняются единицами, а затем – нулями.

. В результате, когда на вход счетчика поступают тактовые импульсы, то в начале все разряды счетчика заполняются единицами, а затем – нулями.

Двоично-десятичные, или декадные счетчики могут быть организованы на бите двоичных счетчиков при помощи взаимной связи между отдельными триггерами, входящими в счетчик.

Шифратор - это комбинационное устройство, преобразующее десятичные числа в двоичную систему счисления, при чем каждому входу может быть поставлено в соответствие десятичное число, а набор выходных логических сигналов соответствует определенному двоичному коду.

Если количество входов настолько велико, что в шифраторе используются все возможные комбинации сигналов на выходе, то такой шифратор называется полным, если не все, то неполным. Число входов и выходов в полном шифраторе связано соотношением N=2m, где N – число входов, m - число выходов.

Рассмотрим пример построения шифратора для преобразования десятиразрядного единичного кода(десятичных чисел от 0 до 9) в двоичный код.

Условное обозначение шифратора и таблица соответствия кода приведены на рисунке

Используя данную таблица соответствия, запишем логические выражения, включая в логическую сумму те входные переменные, которые соответствуют единице некоторой выходной переменной.

Так, на выходе y1 будет логическая единица тогда, когда логическая единица будет или на входе X1, или X3, или X5, или X7, или X9, т.е.

y1= X1+X3+X5+X7+X9.

Аналогично получаем

y2= X2+X3+X6+X7,

y3= X4+X5+X6+X7,

y4= X8+X9.

На рисунке представлена схема такого шифратора, используя элементы ИЛИ.

На практике часто используются шифратор с приоритетом. В таких шифраторах код двоичного числа соответствует наивысшему номеру входа, на который подан сигнал “1”.

Рассмотрим в качестве примера шифратор с приоритетом (приоритетный шифратор) К555ИВ3 серии микросхем К555(ТТЛШ).

Шифратор имеет 9 инверсных входов, обозначенных через PR1,..., PR9.

Аббревиатура PR обозначает “ приоритет”.

Шифратор имеет 4 инверсных выхода B1,..., B8.

Аббревиатура B обозначает “ шина”(от англ. bus).

Основное назначение шифратора – преобразование номера источника сигнала в код (например, номера нажатой кнопки некоторой клавиатуры).

Дешифратором называется комбинационное устройство, преобразующее n-разрядный двоичный код в логический сигнал, появляющийся на том входе, десятичный номер которого соответствует двоичному коду.

Число входов и выходов в так называемом полном дешифраторе связано соотношением m = 2n, где n – число входов, а m - число выходов.Если в работе дешифратора используется неполное число выходов, то такой дешифратор называется неполным.

Обратимся для примера к дешифратору К555ИД6 серии К555.

Дешифратор имеет 4 прямых входа, обозначенных через А1, …, А8.

Аббревиатура А обозначает “адрес”(от лат. adress).

Дешифратор имеет 10 инверсных выходов y0,..., y9.

Благодаря наличию входа разрешения можно наращивать размерность дешифратора. Каскадное соединение дешифраторов.

Преобразователями кодов, в общем случае, предназначенные для преобразования одного кода в другой, при этом часто они выполняют нестандартные преобразования кодов.

Микросхема К155 ПП5 представляет преобразователь двоично-десятичного кода в код семисегментного индикатора.

Мультиплексором называют комбинационное устройство, обеспечивающее передачу в желаемом порядке цифровой информации, поступающей по нескольким входам на один выход.

Мультиплексоры обозначают через MUX (от англ. multiplexor), а также через MS (от англ. multiplexor selector).

Рассмотрим функционирование двухвходового мультиплексора (2 ®1),который условно изображен в виде коммутатора, а состояние его входов Х1 и Х2 и выхода Y приведено в таблице.

Исходя из таблицы, можно записать следующее уравнение:

Y = X1*`A + X2*A.

На рисунке показаны реализация такого устройства И его условное графическое обозначение.

Демультиплексором называют устройство, в котором сигналы с одного информационного входа поступают в желаемой последовательности по нескольким выходам в зависимости от кода на адресных шинах. Таким образом, демультиплексор в функциональном отношении противоположен мультиплексору. Демультиплексоры обозначают через DMX или DMS.

Если соотношение между числом выходов n и числом адресных входов m определяется равенством n = 2m, то такой демультиплексор называется полным, при n < 2m демультиплексор называется неполным.

Рассмотрим функционорование демультиплексора с двумя выходами, который условно изображен в виде коммутатора, а состояние его входов и выходов приведено в таблице.

Из этой таблицы следует:

Y1 = X*`A; Y2 = X*A, т.е. реализовать такое устройство можно так как показано на рисунке.

Для наращивания числа выходов демультиплексора используют каскадное включение демультиплексоров.В качестве примера рассмотрим построение демультиплексоров с 16 выходами (1 ®16) на основе демультиплексоров с 4 выходами (1 ®4).

Цифроаналоговые преобразователи

Цифроаналоговые преобразователи (ЦАП) предназначены для преобразования цифровых сигналов в аналоговые. ЦАП являются “связующим звеном” между аналоговой и цифровой электроникой.

Рассмотрим схему ЦАП с суммированием весовых токов.

Ключ S5 замкнут только тогда, когда разомкнуты все ключи S1... S4 (при этом U вых = 0). U oп – опорное напряжение. Каждый резистор во входной цепи соответствует определенному разряду двоичного числа.

По существу этот ЦАП – инвертирующий усилитель на основе операционного усилителя.

Модуль выходного напряжения пропорционален числу, выходной код которого определяется состоянием ключей S1... S4. Токи ключей суммируются в точке “а”, при чем токи различных ключей различны (имеют разный “вес”).

где Si, i = 1,2,3,4 принимает значения 1, если соответствующий ключ замкнут, и 0, если ключ разомкнут.

Рассмотрим ЦАП на основе резистивной матрицы R - 2R (матрицы постоянного сопротивления)

В схеме использованы так называемые перекидные ключи S1... S4, каждый из которых в одном из состояний подключен к общей точке, поэтому напряжения на ключах невелики. Ключ S5 замкнут только тогда, когда все ключи S1... S4 подключены к общей точке.

Из анализа схемы можно увидеть, что и для нее модуль выходного напряжения пропорционален числу, двоичный код которого определяется состоянием ключей S1…S4.

где Si, i = 1,2,3,4 принимает значения 1, если соответствующий ключ замкнут, и 0, если ключ разомкнут.

Аналогово-цифровые преобразователи (АЦП)

АЦП – устройства, предназначенные для преобразования электрических величин (напряжения, тока, мощности, сопротивления, емкости и т.д.) в цифровой код.

Наиболее часто входной величиной является напряжение. Все другие параметры следует предварительно преобразовать в напряжение.

Виды АЦП и их особенности

В общем случае напряжение характеризуется мгновенными его значениями  , однако можно пользоваться его средними значениями за выбранный промежуток времени

, однако можно пользоваться его средними значениями за выбранный промежуток времени

. В связи с этим, АЦП можно разделить на две группы:

. В связи с этим, АЦП можно разделить на две группы:

1) АЦП мгновенных значений напряжения;

2) АЦП средних значений напряжения.

8.1.1 Интегрирующие АЦП. При преобразовании напряжения в цифровой код исполняются три независимых операций:

§ дискретизация;

§ квантование;

§ кодирование.

При дискретизации непрерывная функция  преобразуется в последовательность ее отсчетов

преобразуется в последовательность ее отсчетов  .

.

Квантование состоит в том, что мгновенные значения функции  ограничиваются только определенными уровнями, которые называются уровнями квантования.

ограничиваются только определенными уровнями, которые называются уровнями квантования.

Кодирование представляет дискретные квантованные величины в виде цифрового кода в последовательности цифр, подчиненных определенному закону.

Дискретизация бывает:

1) равномерная;

2) неравномерная.

При равномерной дискретизации период отсчета  , а при неравномерной – может изменяться. Чаще всего это обусловлено скоростью изменения сигнала. Такая дискретизация называется адаптивной.

, а при неравномерной – может изменяться. Чаще всего это обусловлено скоростью изменения сигнала. Такая дискретизация называется адаптивной.

При дискретизации сигнала появляется погрешность, обусловленная неопределенностью момента времени окончания преобразования. Такая погрешность называется апертурной.

В отличие от дискретизации, которая теоретически является обратимой операцией. Квантование представляет собой необратимое преобразование исходной последовательности и сопровождается появлением неизбежной погрешности. Максимальная погрешность квантования равна ± 5  .

.

В большинстве случаев для оценки качества АЦП не максимальную, а среднеквадратичную погрешность

,

,

что ~ в 3,5 раза ниже максимальной.

В инструкции АЦП используются следующие виды кодов:

1) натуральный двоичный;

2) десятичный.

Основные характеристики АЦП

Основной характеристикой АЦП является его разрешающая способность, которую принято определять величиной, обратной максимальному числу кодовых комбинаций на выходе из АЦП.

Десятиразрядный АЦП обеспечивает погрешность

.

.

Статические характеристики

К статическим характеристикам относят:

§ абсолютные значения и полярность входных сигналов;

§ входное сопротивление;

§ абсолютные значения и полярность выходных сигналов;

§ количество двоичных (десятичных) разрядов выходного сигнала;

§ погрешности преобразования выходного сигнала.

Динамические характеристики

К динамическим характеристикам относят:

§ время преобразования;

§ максимальную частоту дискретизации;

§ апертурное время;

Время преобразования обычно определяют как интервал времени от начала преобразования до появления на выходе АЦП устойчивого кода входного сигнала.

Максимальная частота дискретизации – частота, с которой возможно преобразование входного сигнала при условии, что выбранный параметр (абсолютная погрешность) не выходит за заданные пределы.

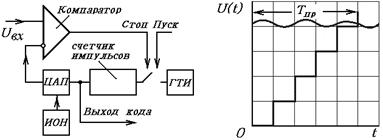

АЦП последовательного счета

Характеризуется как наиболее медленный и дешевый.

Принятые сокращения:

§ ЦАП – цифро-аналоговый преобразователь;

§ ГТИ – генератор тактовых импульсов;

§ ИОН – источник опорного напряжения.

При числе двоичных разрядов счетчика, равном  и периоде следования счетных импульсов

и периоде следования счетных импульсов  максимальное время преобразования можно записать так

максимальное время преобразования можно записать так

.

.

Уравнение преобразования АЦП последовательного счета:

где:  - значение напряжения для одной ступени,

- значение напряжения для одной ступени,  - число ступеней до момента уравнивания величины входного сигнала с выходным сигналом ЦАП.

- число ступеней до момента уравнивания величины входного сигнала с выходным сигналом ЦАП.

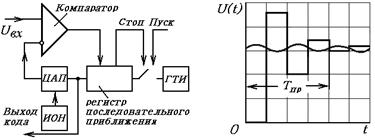

АЦП последовательных приближений

Повышается быстродействие. В основе работы лежит принцип дихотомии (последовательного сравнения преобразуемого напряжения с ½, ¼, 1/8 и т.д. возможного максимального значения  .

.

.

.

Имеет значительно большее быстродействие по отношению к АЦП последовательных приближений при сопоставимой с ним сложности конструкции.

Параллельный АЦП

Самое высокое быстродействие. Преобразователь осуществляет одновременное квантование входного сигнала при помощи набора компараторов, включенных параллельно источнику сигнала.

Пороговые уровни компараторов установлены с помощью резисторного делителя в соответствии со шкалой квантования. Частота дискретизации свыше 100 МГц.

Неоспоримое достоинство параллельных АЦП в виде самого высокого быстродействия уравновешивается существенным недостатком – сложностью и соответственно высокой стоимостью конструкции. Так, для построения 10 разрядного АЦП необходимо разместить на одном кристалле 1023 компаратора с цепями обвязки. Обычно встречаются на практике параллельные АЦП с разрядностью до 8.

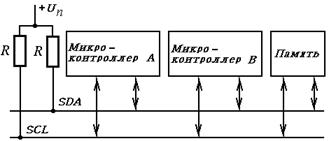

Спецификация шины i 2 C

Полная система управления, состоящая, по крайней мере, из одного микроконтроллера и периферии в виде запоминающих устройств и устройств ввода (вывода), включает в свой состав устройства обмена информацией в виде шинных структур, или шин передачи данных. Стоимость таких систем должна быть минимальна, при выполнении требований

1) обеспечение необходимого быстродействия;

2) быстрые приборы должны иметь возможность обмениваться информацией с медленными.

Шина i2C относится к категории мультимастер шин, что означает, что к ней может быть присоединено больше одного устройства, способного ею управлять.

Терминология шины i2C

§ Передатчик – устройство, которое посылает данные на шину.

§ Приемник – устройство, получающее данные с шины.

§ Ведущий (мастер) – устройство, инициирующее передачу, генерирующее тактовые сигналы и обрывающее передачу.

§ Ведомый – устройство, адресуемое ведущим.

§ Мультимастер – ситуация, когда более одного ведущего может пытаться управлять шиной в одно и то же время без искажения информации.

§ Арбитраж – процедура, гарантирующая, что в ситуации мультимастер только одному ведущему будет позволено управлять шиной и информация не будет искажена.

§ Синхронизация – процедура синхронизации работы во времени двух или более устройств.

Схемы передачи информации

Ситуация одновременной передачи информации двумя устройствами разрешается арбитражем, в результате чего только один мастер выдает управляющий код «1»;, остальные – «0»;.

Линия данных  и линия синхронизации

и линия синхронизации  являются двунаправленными линиями, связанными с положительным напряжением источника питания через подтягивающий резистор.

являются двунаправленными линиями, связанными с положительным напряжением источника питания через подтягивающий резистор.

Когда линия свободна, обе линии находятся в состоянии «1». Выходной каскад устройств, соединенных шиной, должен иметь открытый сток или открытый коллектор для того, чтобы выполнять функцию монтажного И.

Данные на шине I2C могут передаваться со скоростью до 100 бит/с в стандартном режиме или 400 бит/с в быстром режиме.

Генерация тактовых сигналов при передаче данных всегда является обязанностью ведущих, причем каждый из них генерирует свои собственные тактовые сигналы.

Тактовые сигналы могут растягиваться медленными ведомыми, удерживающие в низком состоянии линию синхронизации.

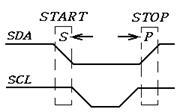

Передача бита

Данные на линии  должны быть стабильны в течение высокого уровня периода тактовой частоты.

должны быть стабильны в течение высокого уровня периода тактовой частоты.

Смена состояния на линии данных происходит только тогда, когда уровень на линии  низкий.

низкий.

Условия старта и остановки:

§ START- условие – это переход из «1» в «0» на линии данных  , если при этом линия синхронизации

, если при этом линия синхронизации  находится в состоянии «1».

находится в состоянии «1».

§ STOP- условие – это переход из«0» в «1» на линии данных  , если при этом линия синхронизации

, если при этом линия синхронизации  находится в состоянии «1».

находится в состоянии «1».

Условия START и STOP всегда генерируется ведущим. Считается, что шина занята после условия START и свободна после условия STOP.

Передача данных

Передача данных осуществляется по формату, указанному на рисунке.

После START- условия (S) посылается адрес ведомого. Это адрес имеет длину 7 бит, за ним следует восьмой бит, который является битом направления данных. (R/  – чтение/запись). «0» означает пердачу данных (WRITE), «1» - запрос данных (READ).

– чтение/запись). «0» означает пердачу данных (WRITE), «1» - запрос данных (READ).

A – подтверждение (низкий уровень SDA);

– нет подтверждения (высокий уровень SDA).

– нет подтверждения (высокий уровень SDA).

Поиск по сайту: