|

АвтоАвтоматизацияАрхитектураАстрономияАудитБиологияБухгалтерияВоенное делоГенетикаГеографияГеологияГосударствоДомДругоеЖурналистика и СМИИзобретательствоИностранные языкиИнформатикаИскусствоИсторияКомпьютерыКулинарияКультураЛексикологияЛитератураЛогикаМаркетингМатематикаМашиностроениеМедицинаМенеджментМеталлы и СваркаМеханикаМузыкаНаселениеОбразованиеОхрана безопасности жизниОхрана ТрудаПедагогикаПолитикаПравоПриборостроениеПрограммированиеПроизводствоПромышленностьПсихологияРадиоРегилияСвязьСоциологияСпортСтандартизацияСтроительствоТехнологииТорговляТуризмФизикаФизиологияФилософияФинансыХимияХозяйствоЦеннообразованиеЧерчениеЭкологияЭконометрикаЭкономикаЭлектроникаЮриспунденкция

ОПТИМАЛЬНЫЙ ДЕМОДУЛЯТОР

ЦЕЛЬ РАБОТЫ

Приобрести и закрепить знания и навыки по применению достижений ТЭС при построении и расчёте основных характеристик систем передачи мультимедийной информации, построенных на основе современных стандартов широкополосного доступа IEEE 802.11 (а,в,д,п), IEEE 802.16 (а,д,е) и других.

| Рис. 1. Блок-схема системы передачи мультимедийной информации |

ИСХОДНЫЕ ДАННЫЕ

ИСХОДНЫЕ ДАННЫЕ

Ширина канала ΔF = 19 МГц

Количество поднесущих частот N = 32

Количество пилотных поднесущих частот Nn=4

Вид модуляции: КАМ-64

Скорость кодирования r =2/3

Вариант № 16

РАСЧЕТНАЯ ЧАСТЬ

Требуется рассчитать:

1) Скорость модуляции и передачи информации на поднесущих, общую скорость передачи информации

1) Скорость модуляции и передачи информации на поднесущих, общую скорость передачи информации

| Рис. 2. Расчет скоростей в MathCAD |

МОДУЛЯТОР

В модуляторе случайный синхронный телеграфный сигнал производит модуляцию гармонического несущего колебания uн(t) = Ucos2πft в соответствии с КАМ-64.

Требуется:

Привести блок-схемы и пояснить принцип работы

Решение:

| Рис.3. Схема модулятора КАМ-64 |

| ФМ-4 |

| ФМ-4 |

| 6дб |

| ∑ |

| Г |

| φ= -π/2 -90° |

| X |

| X |

| X |

| ∑ |

| ∑ |

| X |

| 6дб |

| ∑ |

| ФМ-4 |

| ФМ-4 |

| W0 |

| Z0 |

| Y0 |

| X0 |

| Г |

| φ= -π/2 -90° |

| X |

| X |

| X |

| ∑ |

| ∑ |

| X |

| 6дб |

| ∑ |

| Вход |

| Выход |

| ФМ-4 |

| ФМ-4 |

| X1 |

| Y1 |

| Z1 |

| W1 |

| X2 |

| Y2 |

| Z2 |

| W2 |

| X3 |

| Y3 |

| Z3 |

| W3 |

| ∑ |

| ФМ-4 |

| ФМ-4 |

| 6дб |

| ∑ |

| Рис.4. Сигнальное созвездие модулятора КАМ-64 |

В случае КАМ-64 каждому вектору на комплексной плоскости (комплексному символу модуляции z) соответствует гармоническое колебание, имеющее одно из 64 возможных сочетаний амплитуды и начальной фазы или такое же количество кодовых комбинаций, каждая из которых соответствует определенному варианту гармонического колебания. В случае КАМ-64 такие комбинации содержат по 6 бит информации. При увеличении числа позиций QAM увеличивается пропускная способность канала связи, однако снижается помехоустойчивость, поскольку уменьшаются разности между смежными значениями амплитуд и фаз.

ОПТИМАЛЬНЫЙ ДЕМОДУЛЯТОР

Демодулятор осуществляет когерентную обработку наблюдаемой реализации смеси сигнала и шума

Требуется:

Привести блок-схемы и пояснить принцип работы

Решение:

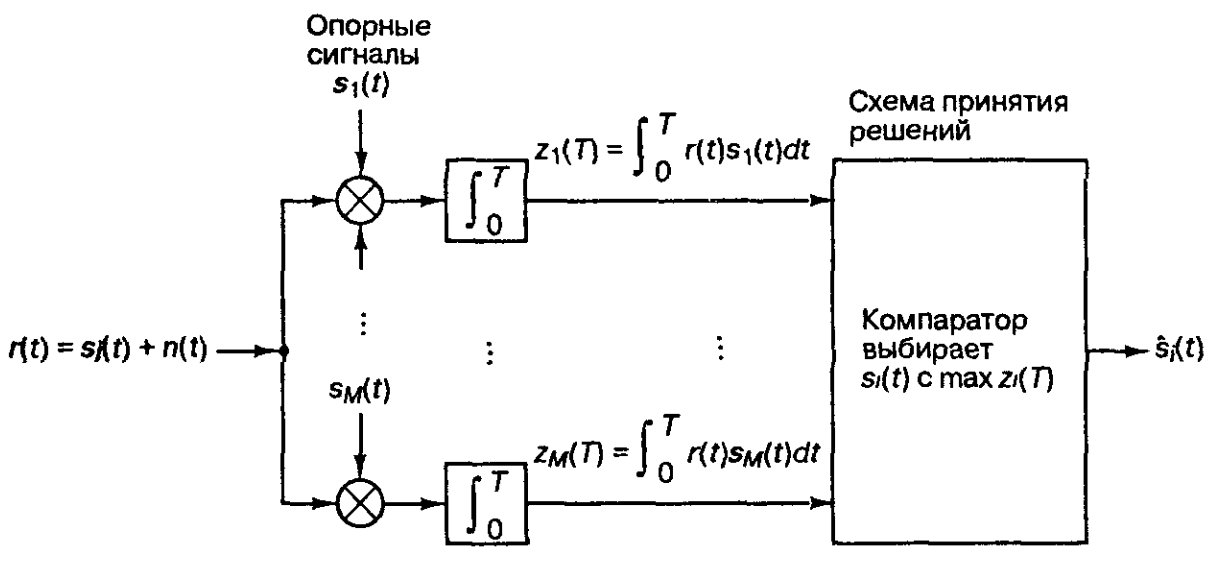

Рис.5 Блок-схема оптимального демодулятора

Демодулятор на каждом тактовом интервале анализирует поступающую на его вход реализацию смеси сигнала и шума z(t) = Si(t) + n(t) по алгоритму, обеспечивающему наилучшее качество приема в соответствии с принятым критерием. Анализ завершается принятием решения в пользу наиболее вероятного переданного на этом такте канального символа(«0» или «1»). В соответствии с принятым решением на выходе модулятора формируется соответствующий уровень напряжения, сохраняемый в течение следующего такта.

ПЕРЕМЕЖИТЕЛЬ

Перемежитель предназначен для борьбы с пакетированием ошибок, использующий перемешивание (перемежение) символов передаваемой последовательности на передаче и восстановление её исходной структуры на приёме. Благодаря перемежению на входе декодера ошибки равномерно распределяются во времени, в идеале образуя поток независимых ошибок.

Требуется:

Привести блок-схемы и пояснить принцип работы

Решение:

| m |

| m |

Рис. 6 Пример схемы перемежителя (М=64)

В тракте передачи содержатся два параллельных канала помехоустойчивого кодирования, называемые каналами высокого и низкого приоритетов. С их помощью организуется иерархический (приоритетный) режим передачи, при котором обеспечивается разная степень защиты передаваемых сигналов в зависимости от способов приёма. В формирователе символов осуществляется объединение  бит в символы путём поочерёдного считывания из каждой ветви по биту.

бит в символы путём поочерёдного считывания из каждой ветви по биту.

ДЕПЕРЕМЕЖИТЕЛЬ

Деперемежитель - это матрица, идентичная перемежителю. Биты из демодулятора считываются в деперемежитель по столбцам, а из деперемежителя построчно, так что каждая из них содержит кодовое слово.

КОДЕР

Кодер выполняет систематическое кодирование с одной проверкой на четность, образуя помехоустойчивый код (k+1,k). Поступающие на вход кодека k-разрядные последовательности информационных символов преобразуются в (k+1)-разрядные кодовые комбинации, в которых к k информационным символам добавляются по одному проверочному символу. Сигнал B(t) на выходе кодера представляет собой случайный синхронный телеграфный сигнал.

Требуется:

Привести блок-схемы и пояснить принцип работы

Решение:

Рис. 7 Пример схемы кодера

Кодер состоит из k q-ичных регистров сдвига с длинами m1.m2,...,mk. Некоторые (может и все) входы регистров и выходы некоторых ячеек памяти соединены с несколькими n сумматорами по модулю q. Число сумматоров больше числа регистров сдвига: n > k.На каждом такте работы кодера на его вход поступает k информационных символов, они вместе с хранящимися в регистрах сдвига символами поступают на входы тех сумматоров, с которыми имеется связь. Результатом сложения является n кодовых символов, готовых к передаче. Затем в каждом регистре сдвига происходит сдвиг: все ячейки сдвигаются вправо на один разряд, при этом крайние левые ячейки заполняются входными символами, а крайние правые стираются. После этого такт повторяется. Начальное состояние регистров заранее известно (обычно нулевое).

Суммарная длина  всех регистров сдвига называется кодовым ограничением, а максимальная длина w = max{m1,...,mk} — задержкой.

всех регистров сдвига называется кодовым ограничением, а максимальная длина w = max{m1,...,mk} — задержкой.

Значения регистров сдвига в каждый момент времени называется состоянием кодера.

ДЕКОДЕР

Декодер канального кода (k+1,k) анализирует принимаемые кодовые комбинации длины k+1 и либо преобразует их в последовательности информационных символов длины k для последующего цифро-аналогового преобразования в уровень отсчета первичного сигнала  , либо отказывается от последующего декодирования, выдавая сообщение об обнаружении ошибки.

, либо отказывается от последующего декодирования, выдавая сообщение об обнаружении ошибки.

Требуется:

Привести блок-схемы и пояснить принцип работы

Решение:

| fD |

| fT |

Рис. 8 Пример схемы декодера.

Использованный код (k+1,k) позволяет гарантированно обнаруживать все ошибки нечетной кратности. Ошибки четной кратности не обнаруживаются. Данный код не позволяет осуществить локализацию обнаруженных ошибок, вследствие чего их исправление невозможно.

Для обнаружения ошибки следует определять количество «1» в принятой (k+1)-разрядной комбинации. Если оно нечетное, то принятая комбинация является запрещенной для данного кода и следует выдать сигнал обнаружения ошибки, в противном случае ошибка не обнаруживается.

Аналитическое выражение для логического сигнала ψ обнаружения ошибки имеет вид:  .

.

ГРАФИКИ

1) Спектральная плотность мощности группового сигнала

Рис. 9 Односторонняя СПМ сигнала.

2) Зависимости средней вероятности ошибки на бит от отношения сигнал/шум на бит без учёта кодирования.

Рис. 10 Зависимость СВО на бит от отношения сигнал/шум на бит без учёта кодирования.

СПИСОК ЛИТЕРАТУРЫ

1. Лекции по ТЭС, Чесноков М. Н.

2. Теория электрической связи, Сальников А. П.

Поиск по сайту: