|

АвтоАвтоматизацияАрхитектураАстрономияАудитБиологияБухгалтерияВоенное делоГенетикаГеографияГеологияГосударствоДомДругоеЖурналистика и СМИИзобретательствоИностранные языкиИнформатикаИскусствоИсторияКомпьютерыКулинарияКультураЛексикологияЛитератураЛогикаМаркетингМатематикаМашиностроениеМедицинаМенеджментМеталлы и СваркаМеханикаМузыкаНаселениеОбразованиеОхрана безопасности жизниОхрана ТрудаПедагогикаПолитикаПравоПриборостроениеПрограммированиеПроизводствоПромышленностьПсихологияРадиоРегилияСвязьСоциологияСпортСтандартизацияСтроительствоТехнологииТорговляТуризмФизикаФизиологияФилософияФинансыХимияХозяйствоЦеннообразованиеЧерчениеЭкологияЭконометрикаЭкономикаЭлектроникаЮриспунденкция

ОТЧЕТ ПО ЛАБОРАТОРНОЙ РАБОТЕ № 1

Информационных технологий и компьютерной безопасности

(факультет)

Кафедра Систем автоматизированного проектирования и информационных систем

ОТЧЕТ ПО ЛАБОРАТОРНОЙ РАБОТЕ № 1

по дисциплине Теория информационных систем

Тема Знакомство с Aldec HDL

Разработали студенты группы ИС121 М.Д. Брик

Подпись, дата Инициалы, фамилия

И.О. Сапич

Подпись, дата Инициалы, фамилия

Руководитель С.И. Короткевич

Подпись, дата Инициалы, фамилия

Защищена ___________________ Оценка _____________________________

дата

Лабораторная работа № 4

«Знакомство с Aldec HDL»

1 Цель работы

Цель работы – получение навыков для работы с отладчиком ALDEC HDL.

2 Используемое оборудование

Для выполнения лабораторной работы используется ПЭВМ типа IBM PC, цветной монитор с графическим адаптером VGA и выше.

3 Краткие теоретические сведения

Aldec HDL транслирует и оптимизирует описания VHDL во внутренний формат, эквивалентный уровню примитивных логических элементов. Этот формат затем компилируется в технологию FPGA.

Когда проект VHDL открывается в FPGA Express, то он преобразуется во внутренний формат базы данных так, чтобы FPGA Express мог синтезировать и оптимизировать его. Когда FPGA Express оптимизирует проект, он может изменить струк-туру частей или всего проекта в целом. Управление идёт лишь степенью реструктуризации.

4 Ход выполнения

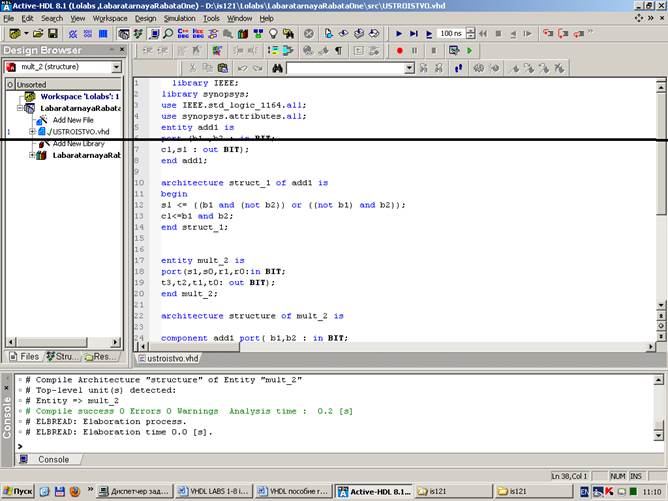

4.1 С помощью текстового редактора набрали описание цифрового устройства в соответствии с полученным вариантом. Для предупреждения ошибок необходимо, чтобы файл имел расширение *.vhd.

4.2 Создать проект в отладчике FPGA Express и подклю-чить к нему набранный файл.

4.3 После корректного подключения файла описания, создать с помощью Aldec HDL отчет по вашему проекту.

5 Результат работы

6. Вывод

В ходе данной лабораторной работы были получены навыки работы с отладчиком ALDEC HDL.

Приложение 1

Листинг

library IEEE;

library synopsys;

use IEEE.std_logic_1164.all;

use synopsys.attributes.all;

entity add1 is

port (b1,b2: in BIT;

cl,sl: out BIT);

end add1;

architecture struct_1 of add1 is

begin

sl <= ((b1 and (not b2)) or ((not b1) and b2));

cl<=b1 and b2;

end struct_1;

entity mult_2 is

port(s1,s0,r1,r0:in BIT;

t3,t2,t1,t0: out BIT);

end mult_2;

architecture structure of mult_2 is

component add1 port(b1,b2: in BIT;

cl,sl: out BIT);

end component;

signal p1,p2,p3,p4: BIT;

begin

t0 <= r0 and s0; -- элемент е1_1

p2 <= r0 and s1; -- элемент е1_3

p1 <= r1 and s0; -- элемент е1_2

p4 <= r1 and s1; -- элемент el_4

circl: add1 port map(p1,p2,p3,t1);

circ2: add1 port map(p3,p4,t3,t2);

end structure;

Поиск по сайту: