|

АвтоАвтоматизацияАрхитектураАстрономияАудитБиологияБухгалтерияВоенное делоГенетикаГеографияГеологияГосударствоДомДругоеЖурналистика и СМИИзобретательствоИностранные языкиИнформатикаИскусствоИсторияКомпьютерыКулинарияКультураЛексикологияЛитератураЛогикаМаркетингМатематикаМашиностроениеМедицинаМенеджментМеталлы и СваркаМеханикаМузыкаНаселениеОбразованиеОхрана безопасности жизниОхрана ТрудаПедагогикаПолитикаПравоПриборостроениеПрограммированиеПроизводствоПромышленностьПсихологияРадиоРегилияСвязьСоциологияСпортСтандартизацияСтроительствоТехнологииТорговляТуризмФизикаФизиологияФилософияФинансыХимияХозяйствоЦеннообразованиеЧерчениеЭкологияЭконометрикаЭкономикаЭлектроникаЮриспунденкция

Программирование прерываний

Сигналы внешних аппаратных прерываний (от таймера, клавиатуры, дисков и проч.) поступают в процессор не непосредственно, а через контроллер прерываний, в качестве которого используется микросхема Intel 8259A. Обработка аппаратного прерывания обязательно включает в себя процедуры управления контроллером прерываний. Организация системы аппаратных прерываний заключается в том, что к восьми входным выводам контроллера подключаются выводы устройств, на которых возникают сигналы прерываний. Выход INT контроллера подключается к одноименному входу микропроцессора. При этом, кроме сигнала INT, инициирующего процедуру прерывания в микропроцессоре, контроллер передает в микропроцессор по линиям данных номер вектора, через который должна быть вызвана программа обработки поступившего прерывания. Передаваемый номер вектора образуется в контроллере путем сложения базового номера, записанного в одном из его регистров, с номером входной линии, по которой поступил запрос. Номер базового вектора заносится в контроллер автоматически в процессе начальной загрузки компьютера. Контроллер программируется через порты 20h и 21h. Поскольку базовый вектор всегда равен 8, то номера векторов, закрепленных за аппаратными прерываниями, лежат в диапазоне 8h,..., Fh.

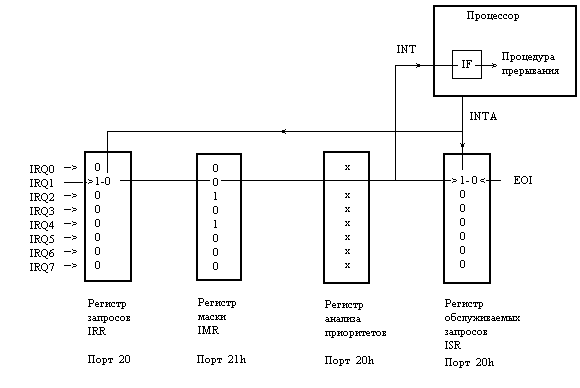

Во внутренней структуре контроллера можно выделить четыре основных узла: регистр входных запросов, регистр маски, схему приоритетов и регистр обслуживаемых запросов (Рисунок 1). Все узлы контроллера восьмибитовые, по одному биту на каждый входной сигнал.

Сигнал запроса прерывания IRQ от устройства поступает на вход регистра запросов и устанавливает в 1 соответствующий бит этого регистра. Далее на пути сигнала стоит регистр маски, программируемый через порт 21h. Значение в бите маски разрешает прохождение сигнала, значение 1 - запрещает. Пройдя через маску, сигнал поступает на схему анализа приоритетов. При стандартной настройке схемы приоритетов, приоритеты сигналов IRQ снижаются по мере роста номера сигнала. Пройдя через схему анализа приоритетов, сигнал запроса прерывания поступает на вход регистра обслуживаемых запросов и дает разрешение на установку в 1 его бита (однако не устанавливает его).

Рисунок 1 - Логическая структура контроллера прерываний

Одновременно сигнал поступает на вход INT микропроцессора, который регистрирует поступление сигнала INT лишь в случае, если установлен флаг разрешения прерываний IF в регистре флагов. Сброс флага IF командой CLI запрещает все аппаратные прерывания. Микропроцессор, получив сигнал INT, отзывается на него выходным сигналом INTA, который поступает в контроллер прерывания и выполняет там два действия. Во-первых, он устанавливает бит регистра обслуживаемых запросов, разрешенный сигналом запроса прерывания. Во-вторых, он сбрасывает бит регистра запросов.

Микропроцессор, одновременно с посылкой в контроллер прерываний сигнала INTA сбрасывает флаг IF в регистре флагов, запрещая все аппаратные прерывания. Прерывания останутся запрещенными до выполнения пользователем команды STI или до установки флага IF каким-либо другим способом.

Установка 1 в бите регистра обслуживаемых запросов воздействует на схему анализа приоритетов. Установленный бит блокирует в схеме анализа приоритетов все уровни прерываний, начиная с текущего и ниже. Таким образом, если не принять специальных мер, даже после завершения обработки прерывания все, прерывания данного и более низких приоритетов останутся заблокированными. Сброс бита регистра обслуживаемых запросов осуществляется посылкой кода 20h в порт 20h. Этот код получил название команды или приказа EOI (End Of Interrupt). Команда EOI должна быть в любой программе по обработке прерываний.

Практически структуру программы обработки прерываний выбирают, исходя из конкретных условий. Часто в самом начале программы выполняют команду STI, чтобы не задерживать обработку прерываний от более приоритетных устройств (в частности, таймера). Приказ конца прерывания EOI посылается в контроллер в самом конце программы, перед завершающей командой IRET с тем, чтобы полностью исключить вложенные прерывания от запросов того же уровня. Однако сигнал прерывания того же (или более низкого уровня) может пройти между командами, реализующими приказ EOI, и командой IRET, что вызовет повторный вход в эту же программу. Чтобы избежать этого, перед командой EOI выполняют команду запрета всех прерываний CLI. Команда IRET не только восстанавливает адрес возврата в регистрах CS и IP, но и содержимое регистра флагов на момент прерывания.

Типичные структуры программы обработки прерываний:

а) STI б)

.....

CLI

MOV AL,20h; Команда MOV AL,20h; Команда

OUT 20h,AL; EOI OUT 20h,AL; EOI

IRET IRET

при разрешенных вложенных прерываниях (а) и при запрещенных вложенных прерываниях (б).

При отладке взаимодействия с компьютером аппаратуры, работающей в режиме прерываний, приходится анализировать содержимое внутренних регистров контроллера прерываний. Для этого существуют специальные команды контроллера.

Поиск по сайту: