|

АвтоАвтоматизацияАрхитектураАстрономияАудитБиологияБухгалтерияВоенное делоГенетикаГеографияГеологияГосударствоДомДругоеЖурналистика и СМИИзобретательствоИностранные языкиИнформатикаИскусствоИсторияКомпьютерыКулинарияКультураЛексикологияЛитератураЛогикаМаркетингМатематикаМашиностроениеМедицинаМенеджментМеталлы и СваркаМеханикаМузыкаНаселениеОбразованиеОхрана безопасности жизниОхрана ТрудаПедагогикаПолитикаПравоПриборостроениеПрограммированиеПроизводствоПромышленностьПсихологияРадиоРегилияСвязьСоциологияСпортСтандартизацияСтроительствоТехнологииТорговляТуризмФизикаФизиологияФилософияФинансыХимияХозяйствоЦеннообразованиеЧерчениеЭкологияЭконометрикаЭкономикаЭлектроникаЮриспунденкция

Проектування лічильників зі зворотними зв’язками

1 Паралельні лічильники. Двійкові лічильники утворюються за допомогою прямих міжрозрядних зв’язків – з виходів попередніх на входи наступних розрядів. Запровадженням зворотних зв’язків – з виходів наступних розрядів на входи попередніх – можна блокуванням перенесень усунути будь-які надлишкові стани, отже, дістати лічильники з довільним модулем і порядком лічби. Якщо будувати в такий спосіб лічильники з послідовним або комбінованим переносом між окремими розрядами, потрібно визначати функції збудження як інформаційних, так і синхровходів тригерів.

Тут розглядатимемо паралельні лічильники, синхровхід усіх розрядів яких є спільний, тому достатньо знайти функції збудження лише інформаційних входів. Перевагою паралельних лічильників крім високої швидкодії є також відсутність проміжних станів під час переходів вихідного коду, як видно з часових діаграм перемикань лічильника, наприклад, з модулем М = 5, наведених на рис. 3.11.

Приклад 1. Методику проектування розглянемо на прикладі паралельного лічильника з модулем М = 5 і природним порядком лічби.

|

Рис. 3.11

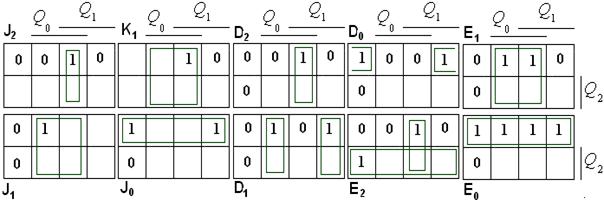

1) За потрібною кількістю розрядів n = 3 у перемикальній таблиці (рис. 3.12,а) заповнюємо колонки початкового Qі та наступного по надходженні лічильного імпульсу Qі + станів тригерів з урахуванням того, що коди N = 5... 7 є надлишкові.

2) Вибираємо тип тригерів (для прикладу розглянемо варіанти лічильника на JK-, D- та TE-тригерах) та заповнюємо стовпці таблиці для функцій збудження на їх інформаційних входах. Так, JK-тригерові старшого розряду колонкам Q 2 Q 2+ лівої частини таблиці відповідають колонки J 2 K 2 її правої частини. Тому для переходів Q 2 Q 2+ = 00, 01, 10 вносимо значення J 2 K 2 = 0Х, 1Х, Х1, відтак аналогічно заповнюємо колонки для всіх інших розрядів згідно з таблицею переходів JK-тригера. Для розрядів на D-три- герах вносимо значення Dі = Qі +, а на ТЕ-тригерах занотовуємо Еі = 0, якщо тригер не перемикається та Еі = 1, якщо перемикається.

3) Безпосередньо з таблиці довизначенням Х = 1 маємо К 2 = К 0 = 1, а інші функції збудження мінімізуємо за діаграмами термів (на рис. 3.12, б порожнім клітинкам відповідають факультативні значення Х):

4) З’єднуючи синхровходи тригерів зі спільним лічильним входом С, а інші входи – згідно з функціями збудження, отримуємо варіанти реалізації лічильника на JK-, D- i TE-тригерах (рис. 3.12, в, г, ґ відповідно). Такі лічильники є синхронні, бо всі розрядні тригери перемикаються одночасно (див. рис. 3.11).

Найпростіший щодо реалізації варіант визначається елементною базою. Так, лічильники на JK-тригерах з дубльованими входами потребують мінімуму додаткових елементів у міжрозрядних зв’язках (при викори- станні інверсного виходу і подвійних входів у старшому розряді схема на рис. 3.12,в не містить таких елементів) і можуть виявитися зручними для побудови на ІС жорсткої структури. На програмованих ІС економічнішими є схеми на D- і RSC-тригерах з динамічним керуванням. Крім того, для низки застосувань доцільною є побудова лічильників з довільним модулем і порядком лічби за схемами з послідовним і комбінованим переносом.

|

а

|

б

Рис. 3.12

2Реверсивні лічильники. У колах стеження, зокрема, компенсаційних приладів, аналогово цифрових перетворювачів в окремі інтервали часу лічильник має працювати на додавання, а в інші інтервали – на віднімання.

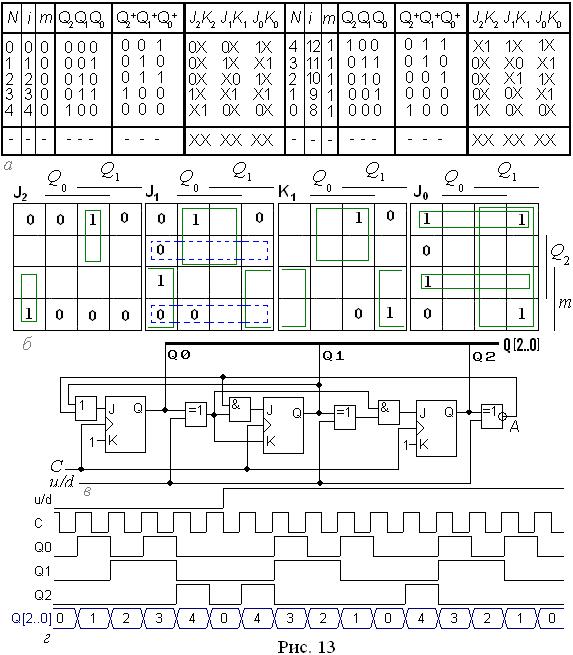

Приклад 2. Особливості проектування розглянемо на прикладі побудовипаралельного лічильника з керованим напрямком лічби, модулем М = 5 і природним порядком лічби на JK-тригерах. Перемикальну таблицю (див. рис. 3.12, а) доповнюємо стовпцем модифікації схеми (рис. 3.13, а): при m = 0 лічильник працює в режимі додавання, а при m = 1 – в режимі віднімання, а також стовпцем десяткового коду набору змінних i = mQ 2 Q 1 Q 0. В іншому методика проектування аналогічна.

Приклад 2. Особливості проектування розглянемо на прикладі побудовипаралельного лічильника з керованим напрямком лічби, модулем М = 5 і природним порядком лічби на JK-тригерах. Перемикальну таблицю (див. рис. 3.12, а) доповнюємо стовпцем модифікації схеми (рис. 3.13, а): при m = 0 лічильник працює в режимі додавання, а при m = 1 – в режимі віднімання, а також стовпцем десяткового коду набору змінних i = mQ 2 Q 1 Q 0. В іншому методика проектування аналогічна.

Безпосередньо з таблиці маємо К 2 = К 0 = 1, а інші функції збудження дістанемо з діаграм термів (на рис. 13,б порожнім клітинкам відповідають факультативні значення Х), застосовуючи прийоми їх сумісної мінімізації:

Цим рівнянням відповідає схема лічильника (рис. 3.13,в), напрямок лічби якого керується сигналом u/d = m (рис. 3.13,г).

Поиск по сайту: