|

АвтоАвтоматизацияАрхитектураАстрономияАудитБиологияБухгалтерияВоенное делоГенетикаГеографияГеологияГосударствоДомДругоеЖурналистика и СМИИзобретательствоИностранные языкиИнформатикаИскусствоИсторияКомпьютерыКулинарияКультураЛексикологияЛитератураЛогикаМаркетингМатематикаМашиностроениеМедицинаМенеджментМеталлы и СваркаМеханикаМузыкаНаселениеОбразованиеОхрана безопасности жизниОхрана ТрудаПедагогикаПолитикаПравоПриборостроениеПрограммированиеПроизводствоПромышленностьПсихологияРадиоРегилияСвязьСоциологияСпортСтандартизацияСтроительствоТехнологииТорговляТуризмФизикаФизиологияФилософияФинансыХимияХозяйствоЦеннообразованиеЧерчениеЭкологияЭконометрикаЭкономикаЭлектроникаЮриспунденкция

Елементи технічного проектування

Вже на стадії логічного проектування потрібно враховувати можливості елементної бази щодо схемної реалізації синтезованої структурної функції. Це врахування може спричинити перетворення функції до такого виразу, який технічно можна втілити на ІС вибраної серії. Крім виконуваних елементами серії логічних функцій доводиться зважати й на такі особливості, які стосуються технічного проектування. Розглянемо основні з них.

1 Врахування швидкодії логічних елементів. Логічний елемент умовно можна моделювати двома частинами: безінерційною, що виконує логічну функцію, наприклад, інверсію (рис. 1.5, а), та елементом затримки D (Delay –затримка), який відображає перехідні процеси (рис. 1.5, б) усталення вихідного сигналу. Тривалість перехідних процесів відлічується відносно порогової напруги U п спрацьовування елемента й оцінюється часом затримки поширення сигналу t 10з.п під час переходу вихідної напруги від рівня лог. 1 – U 1 до рівня лог. 0 – U 0 та часом затримки поширення t 01з.ппід час перемикання в протилежному напрямку. За ланцюжкового сполучення елементів зручно користуватися усередненим параметром – середнім часом затримки поширення t з.п = = 0,5(t 10з.п + t 01з.п), а часові діаграми зображати ідеалізовано (рис. 1.5, в). Часові інтервали на них позначатимемо цифрами, які вказують на тривалість у кількості середніх затримок t з.п.

Умовна дискретизація перехідних процесів у часі дозволяє спростити підрахунок шви-дкодії ЦП до виразу: t у = Nt з.п, де t у – час усталення сигналу на виході пристрою, N – максимальна кількість однотипних елементів на шляху поширення його від входу до виходу. Наприклад, час усталення в елементі Виключне АБО (див. рис. 1.4, ґ) визначається затримкою трьох елементів І-НЕ. Для наочності шлях поширення сигналу позначатимемо його двійковими кодами безпосередньо на схемі (рис. 1.5, г). У першій позиції кодів наведено початковий стан схеми при х 1 = 0, х 2 = 1. У другій позиції нульовим індексом вгорі х 1 = 10 зазначено, що від зміни цього рівня на вході починається відлік затримки поширення сигналу на шляху: х 1® DD1 ® DD3 ® DD4 ® у, тому на виході елемента DD1 індексом 1 позначено одну затримку t з.п, на виході DD3 – дві затримки і, нарешті, на виході у – три затримки. На часових діаграмах (рис. 1.5, ґ) цей процес відображено, починаючи з моменту t 1.

Аналогічно відбувається перехідний процес по зміні рівня на другому вході до х 2 = 0, як зазначено кодами в третій позиції станів і на діаграмах у момент t 2. Отже, час усталення пристрою під час перемикання в обох напрямках становить t у = 3 t з.п. При зображенні логічного виразу в універсальних базисах І-НЕ чи АБО-НЕ час усталення можна підрахувати за найбільшою кількістю інверсій над аргументами.

Таким чином, час усталення ЦП визначається не тільки швидкодією елементів, але й глибиною реалізації схеми. Реалізація за первісними після мінімізації термами є двоступеневою (див. рис. 1.4, є), якщо вхідні сигнали вважати двофазними, отже, має найвищу швидкодію. Спрощення схеми шляхом каскадування поряд із перевагою – ощадливістю обладнання – призводить одночасно до погіршення швидкодії. Так, схема на рис. 1.4, ж має більшу глибину реалізації – є вже триступеневою. Якщо каскадна реалізація не задовольняє вимоги швидкодії, доводиться повертатися до двоступеневої реалізації з більшою складністю схеми.

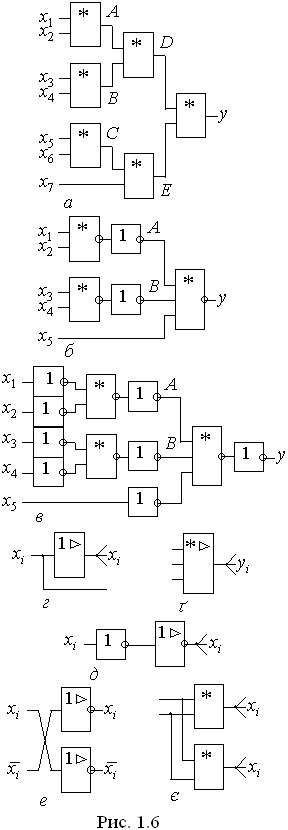

2 Врахування коефіцієнта об'єднання. Якщо в елементі бракує входів для реалізації терма, вдаються до багатоступеневих (деревоподібних) схем нарощування коефіцієнта об'єднання. Елементи без інверсії на виході каскадуються за схемою на рис. 1.6, а, де позначка * вказує на двомісну операцію І, АБО чи суми за модулем два. Так, коефіцієнт об'єднання m = 7 на двовходових елементах І утворюється за формулою:

яка потребує m – 1 = 6 елементів.

Принцип об'єднання елементів з інверсією на виході (І-НЕ, АБО-НЕ) для виконання логічної функції, однойменної з назвою елемента (рис. 1.6, б), покажемо на прикладі операції І-НЕ для m =5:

де подвійна риска означає, що одна інверсія виконується елементом І-НЕ, а друга – додатковим інвертором. При виконанні функції, протилежної назві елемента (у базисі І-НЕ виконується функція АБО-НЕ чи в базисі АБО-НЕ – функція І-НЕ), об'єднання ще більш ускладнюється (рис. 1.6, в), наприклад,

Багатоступеневими схемами можна реалізувати довільні коефіцієнти об'єднання, проте з погіршенням швидкодії і додатковими витратами елементів. Цей недолік послаблюється застосуванням модифікованих елементів з розширеними функціональними можливостями або реалізацією у мішаному базисі шляхом перетворення функцій.

3 Врахування коефіцієнта розгалуження. Навантаження на кожне джерело зовнішнього вхідного сигналу або на елемент-джерело внутрішньої змінної, яка є функцією зовнішніх аргументів, легко підраховується за кількістю входжень тієї чи тієї змінної до структурної функції проектованої логічної схеми. Якщо ця кількість перевищує припустимий коефіцієнт розгалуження джерела, уживають заходів щодо його розвантаження.

3 Врахування коефіцієнта розгалуження. Навантаження на кожне джерело зовнішнього вхідного сигналу або на елемент-джерело внутрішньої змінної, яка є функцією зовнішніх аргументів, легко підраховується за кількістю входжень тієї чи тієї змінної до структурної функції проектованої логічної схеми. Якщо ця кількість перевищує припустимий коефіцієнт розгалуження джерела, уживають заходів щодо його розвантаження.

Передусім, за допомогою додаткового елемента на вході, який відіграє роль підсилювача (рис. 1.6, г), розв'язують джерело сигналу від навантажувальних елементів, а всередині проектованої схеми при цьому замість звичайного застосовують елемент із підвищеною навантажувальною здатністю (рис. 1.6, ґ).

Якщо використовують підсилювальні елементи з інверсним виходом, відновлення аргументу здійснюють шляхом подвійного інвертування (рис. 1.6, д), а у випадку парафазних сигналів достатньо й одного інвертування (рис. 1.6, е). Для запобігання погіршенню швидкодії через затримку в додаткових розвантажувальних елементах уживають спосіб дублювання елемента (рис. 1.6, є), якщо він сам не перевантажує сигнал.

4 Врахування небезпечних змагань сигналів. З огляду на неоднакові затримки в попередніх елементах і різні шляхи поширення виникають так звані змагання сигналів: вони потрапляють до входів пристрою неодночасно. Внаслідок цього можуть утворюватися сигнали, не передбачені за правильної роботи пристрою – ризики, зокрема, імпульсні завади. У такому разі змагання є небезпечними. Якщо, наприклад, до входів елемента І-НЕ (рис. 1.7, а) перепади сигналів х 1, х 2 потрапляють одночасно (рис. 1.7, б) або негативний фронт випереджає позитивний (рис. 1.7, в), то на виході у ризики відсутні, а якщо, навпаки, позитивний фронт випереджає негативний, виникає ризик – імпульсна завада тривалістю ti (рис. 1.7, г), яка може спричинити хибне спрацьовування навантажувальних елементів. Не важко переконатися самостійно, що в елементах АБО-НЕ ризик виникає за протилежного положення фронтів вхідних сигналів.

Для усунення небезпечних змагань можна передбачити такий порядок зміни рівнів, коли паразитний викид стає дуже коротким або не виникає зовсім, наприклад, штучною затримкою сигналу х 1, як на рис. 1.7, в. Проте у відносно складних ЦП запобігти ризикам таким чином важко, тому вдаються до схемних засобів їх усунення. Якщо в окремі моменти часу можлива зміна лише одного вхідного сигналу, то є змога виконати логічну схему, вільну від небезпечних змагань. Умовою цього є зв'язність сполук на діаграмі термів: усі сусідні одиничні клітинки мають бути об'єднаними хоча б однією сполукою, для чого слід ввести додаткові сполуки, тобто ускладнити схему.

Проте найчастіше застосовують синхронізацію пристроїв: спрацьовування елементів визначаються моментами надходження синхроімпульсів, період яких вибирається таким, щоб перехідні процеси усталення рівнів устигли закінчитись. Згідно з рис. 1.7, г зчитуванням вхідної інформації синхроімпульсом після інтервалу ti можна позбутися паразитного викиду.

Заваду можна зменшити до припустимого рівня також за допомогою згладжувального фільтра типу інтегрувального кола (пунктир на рис. 1.7, а). Проте через погіршення швидкодії такого заходу вживають рідко, в основному, для виявлення місця виникнення завади: якщо з приєднанням до виходу у невеликої ємності викид зменшується (пунктир на рис. 1.7, г), слід усунути змагання сигналів на входах елемента.

Поиск по сайту: