|

АвтоАвтоматизацияАрхитектураАстрономияАудитБиологияБухгалтерияВоенное делоГенетикаГеографияГеологияГосударствоДомДругоеЖурналистика и СМИИзобретательствоИностранные языкиИнформатикаИскусствоИсторияКомпьютерыКулинарияКультураЛексикологияЛитератураЛогикаМаркетингМатематикаМашиностроениеМедицинаМенеджментМеталлы и СваркаМеханикаМузыкаНаселениеОбразованиеОхрана безопасности жизниОхрана ТрудаПедагогикаПолитикаПравоПриборостроениеПрограммированиеПроизводствоПромышленностьПсихологияРадиоРегилияСвязьСоциологияСпортСтандартизацияСтроительствоТехнологииТорговляТуризмФизикаФизиологияФилософияФинансыХимияХозяйствоЦеннообразованиеЧерчениеЭкологияЭконометрикаЭкономикаЭлектроникаЮриспунденкция

Синхронні шини

|

Читайте также: |

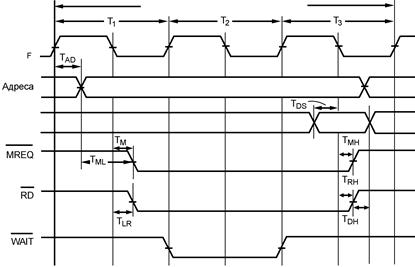

Як приклад того, як працює асинхронна шина, розглянемо тимчасову діаграму на рис. 6.3. В даному прикладі ми використовуватимемо задаючий генератор на 40 Мгц, який дає цикл шини в 25 нc. Хоча може здатися, що шина працює поволі в порівнянні з процесорами на 500 Мгц і вище, не багато сучасних шин працюють швидше. Наприклад, шина ISA (вона вбудована у всі персональні комп'ютери з процесором Intel) працює з частотою 8,33 Мгц, і навіть популярну шину PCI — з частотою 33 Мгц або 66 Мгц. Причини такої низької швидкості сучасних шин були дані вище: такі технічні проблеми, як перекіс шини і вимога сумісності.

У нашому прикладі ми припускаємо, що прочитування інформації з пам'яті займає 40 не з тієї миті, як адреса стала постійною. Як ми скоро побачимо, знадобиться три цикли шини, щоб рахувати одне слово. Перший цикл починається на наростаючому фронті відрізка Т1 а третій закінчується на наростаючому фронті відрізка Т3, як показано на рис. 6.3. Відзначимо, що жоден з наростаючих і задніх фронтів не намальований вертикально, тому що жоден електричний сигнал не може змінювати своє значення за нульовий час. У нашому прикладі ми припускаємо, що для зміни сигналу потрібно 1 не. Генератор і лінії ADDRESS, DATA, МКЩ, КГ), WAIT показані в тому ж масштабі часу.

|

Рис. 6.3 – Тимчасова діаграма процесу прочитування на синхронній шині

T1 визначається наростаючим фронтом генератора. За частину часу T1 центральний процесор поміщає адресу потрібного слово на адресні лінії. Оскільки адреса є не одним значенням (на відміну від генератора), ми не можемо показати його у вигляді однієї лінії на схемі. Натомість ми показали його у вигляді двох ліній з перетинами там, де ця адреса міняється. Сірий колір на схемі показує, що у цей момент не важливо, яке значення прийняв сигнал. Використовуючи ту ж угоду, ми бачимо, що зміст ліній даних не має значення до відрізка Т3.

Після того, як у адресних ліній з'являється можливість придбати нове значення, встановлюються сигнали MREQ і RD. Перший указує, що здійснюється доступ до пам'яті, а не до пристрою вводу-виводу, а другий — що здійснюється читання, а не запис. Оскільки прочитування інформації з пам'яті займає 40 не після того, як адреса стала постійною (частина першого циклу), пам'ять не може передати необхідні дані за період Т* Щоб центральний процесор не чекав надходження даних, пам'ять встановлює лінію WAIT на початку відрізка Тг. Ця дія вводить періоди очікування (додаткові цикли шини), доти поки пам'ять не скине сигнал WAIT. У нашому прикладі вводиться один період очікування (Тг), оскільки пам'ять працює дуже поволі. На початку Т3, коли є упевненість в тому, що пам'ять одержить дані протягом поточного циклу, сигнал WAIT скидається.

Під час першої половини Т3 пам'ять поміщає дані на інформаційні лінії. На задньому фронті Т3 центральний процесор стробує (тобто прочитує) інформаційні лінії, зберігаючи їх значення у внутрішньому регістрі. Прочитавши дані, центральний процесор скидає сигнали MREQ, і Кв. У разі потреби на наступному наростаючому фронті може початися ще один цикл пам'яті.

Далі вияснюється значення восьми символів на тимчасовій діаграмі (див. рис. 6.3). TAD> наприклад, — це часовий інтервал між наростаючим фронтом Ti і установкою адресних ліній. Відповідно до вимог синхронізації Tad Ј 11 не. Означає, виробник процесора гарантує, що під час будь-якого циклу прочитування центральний процесор видаватиме необхідну адресу в межах 11 не від середини наростаючого фронту Tj.

Умови синхронізації також вимагають, щоб дані поступали на інформаційні лінії принаймні за 5 не (Tds) до заднього фронту Тз, щоб дати даним час встановитися до того, як процесор стробує їх. Поєднання обмежень на TAD і TDS означає, що у гіршому разі у розпорядженні пам'яті буде тільки 62,5— 11—5=е46>5 не з моменту появи адреси і до моменту, коли потрібно видавати дані. Оскільки достатньо 40 не, пам'ять навіть в найгіршому випадку може завжди відповісти за період Т3. Якщо пам'яті для прочитування потрібно 50 не, то необхідно ввести другий період очікування, і тоді пам'ять відповість протягом Т3. Вимоги синхронізації гарантують, що адреса буде встановлена принаймні за 6 не до того, як з'явиться сигнал MREQ. Цей час може бути важливо в тому випадку, якщо MREQ запускає вибір елементу пам'яті, оскільки деякі типи пам'яті вимагають деякого часу на установку адреси до вибору елементу пам'яті. Ясно, що розробнику системи не слід вибирати мікросхему пам'яті, на установку якої потрібно 10 не.

Обмеження на Тм і TLR означають, що WREQ і RD будуть встановлені в межах 8 не від заднього фронту Tt. У гіршому разі у мікросхеми пам'яті після установки MREQ і Ш5 залишиться всього 25+25-8-5=37 не на передачу даних по шині. Це обмеження додатково по відношенню до інтервалу в 40 не і не залежить від нього.

ТMH і TRH визначають, скільки часу потрібний на відміну сигналів MREQ і RI5 після того, як дані стробовані. Нарешті, TDH визначає, скільки часу пам'ять повинна тримати дані на шині після зняття сигналу І). У нашому прикладі при даному процесорі пам'ять може видалити дані з шини, як тільки скидається сигнал RD; при інших процесорах, проте, дані можуть зберігатися ще якийсь час.

Необхідно підкреслити, що наш приклад є сильно спрощеною версією реальних тимчасових обмежень. Насправді повинно визначатися значно більше таких обмежень. Проте цей приклад наочно демонструє, як працює синхронна шина.

Відзначимо, що сигнали управління можуть задаватися або за допомогою низького, або за допомогою високої напруги. Що є зручнішим у кожному конкретному випадку, повинен вирішувати розробник, хоча, по суті» вибір довільний.

Поиск по сайту: