|

АвтоАвтоматизацияАрхитектураАстрономияАудитБиологияБухгалтерияВоенное делоГенетикаГеографияГеологияГосударствоДомДругоеЖурналистика и СМИИзобретательствоИностранные языкиИнформатикаИскусствоИсторияКомпьютерыКулинарияКультураЛексикологияЛитератураЛогикаМаркетингМатематикаМашиностроениеМедицинаМенеджментМеталлы и СваркаМеханикаМузыкаНаселениеОбразованиеОхрана безопасности жизниОхрана ТрудаПедагогикаПолитикаПравоПриборостроениеПрограммированиеПроизводствоПромышленностьПсихологияРадиоРегилияСвязьСоциологияСпортСтандартизацияСтроительствоТехнологииТорговляТуризмФизикаФизиологияФилософияФинансыХимияХозяйствоЦеннообразованиеЧерчениеЭкологияЭконометрикаЭкономикаЭлектроникаЮриспунденкция

Обнаружение неисправностей в схемах с памятью

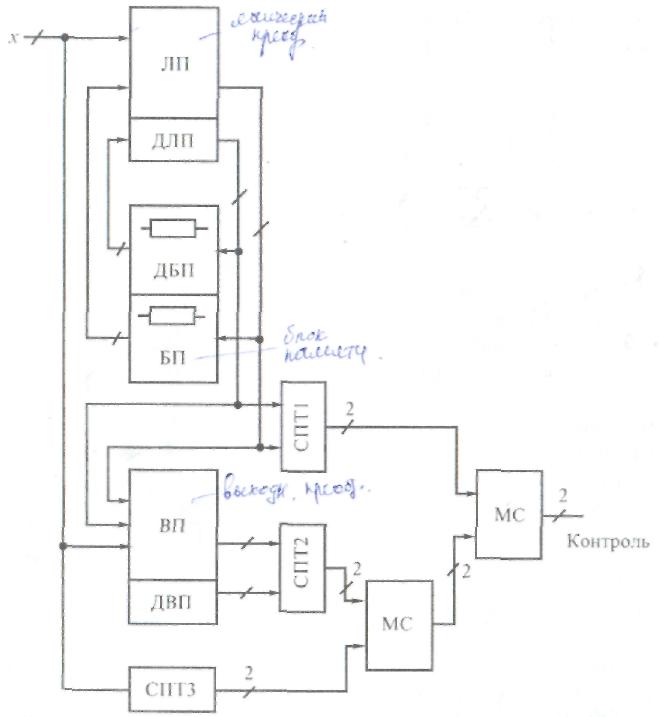

На рис. 6.56 приведена с труктура многотактной схемы с обнаружением отказов. Комбинационная часть схемы разделена на два блока. Логический преобразователь (ЛП) реализует функции включения элементов памяти (ЭП), составляющих блок памяти (БП), а выходной преобразователь (ВП) — функции выходов.

Для организации контроля в схему вводятся дополнительные ЭП (блок ДБП) с таким расчётом, чтобы векторы y 1, y 2,... y m, y'm +1, y'm +2, …, y'm +k, соответствующие рабочим внутренним состояниям схемы, являлись словами какого-либо кода с обнаружением ошибок. При этом разряды вектора y 1, y 2,... y mсоответствуют основным ЭП, расположенным в блоке БП, а разряды y'm +1, y'm +2, …, y'm +k– дополнительным ЭП, расположенным в блоке ДБП. Для управления дополнительными ЭП формируется дополнительный логический преобразователь (блок ДЛП). Для контроля ВП используется другой код с обнаружением ошибок. При этом могут вводиться дополнительные контрольные выходы схемы, реализуемые дополнительным выходным преобразователем (блок ДВП).

Неисправности элементов блоков ЛП и БП приводят к искажению вектора y 1, y 2 ,..., y'm +kхарактеризующего состояние системы элементов памяти, что фиксируется самопроверяемым тестером СПТ1. Тестер СПТ2 контролирует исправное состояние блоков ВП и ДВП. Если на вход схемы информация поступает также в виде слов кода с обнаружением ошибок, то последний контролируется при помощи СПТ3. Парафазные выходы всех тестеров объединяются посредством модуля сравнения МС, в результате чего образуется единый парафазный выход контроля.

На рис. 6.57 приведена структура самопроверяемой самодвойственной многотактной схемы. Логический и выходной преобразователи, являющиеся комбинационными схемами, преобразуются в самодвойственные схемы в соответствии с рис. 6.46. В образованной схеме ЛП описывается СД-функциями y* 1, y* 2,..., y*m, а ВП – самодвойственными функциями z* 1, z* 2,..., z*p. Линии задержки (ЛЗ) дублируются. Каждая ЛЗ осуществляет задержку на время, равное половине периода импульсной последовательности а (см. рис. 6.40).

Самодвойственные сигналы, формируемые на выходах блока ВП, при помощи схемы сжатия сводятся к одному контрольному сигналу z *. Неисправности элементов ЛП и линий задержки приводят к появлению несамодвойственных сигналов на входах ВП, что фиксируется по выходу z *.

Рис. 6.56 – Структура многотактной схемы с обнаружением отказов

Рис. 6.57 – Структура самопроверяемой самодвойственной многотактной схемы

42. Организация тестового диагностирования МПС

Микропроцессорная система как объект диагностики представляет собой сложную вычислительную структуру с шинной организацией. Она состоит из четырех основных групп БИС, микропроцессора, памяти, контроллеров ввода-вывода и контроллеров связи с объектами. Каждая из этих функциональных подсистем, в свою очередь, является достаточно сложной с точки зрения диагностирования. Поэтому при организации тестового и функционального диагностирования микропроцессорных систем используется декомпозиционный подход, при котором в качестве объекта диагностирования выступают отдельные функциональные устройства: АЛУ, процессор, ОЗУ, устройства ввода-вывода УВВ, отдельные ТЭЗы и корпуса СИС и БИС. Трудности, возникающие при диагностировании микропроцессорных систем, определяются высокой степенью интеграции БИС (большим числом логических элементов и ограниченным числом внешних контактов), разветвленными связями между элементами системы. Кроме того, разработчик аппаратуры очень часто не имеет полной информации о внутренней структуре БИС и вынужден рассматривать ее как «черный» ящик.

По этим причинам хорошо развитые общие методы построения тестов цифровых схем не всегда могут быть эффективно использованы. Для тестирования микропроцессоров разрабатываются и специальные методы, основанные на применении функциональных тестов. Эти тесты обеспечивают выполнение операций микропроцессора на некотором множестве операндов.

Существуют три основных подхода к построению тестов микропроцессоров и микропроцессорных систем: модульный, микропрограммный и функциональный. При модульном подходе БИС представляется как набор функционально законченных модулей, таких как регистры, счетчики, сумматоры, АЛУ, мультиплексоры и др. Для каждого модуля строится частный тест. Общий тест образуется путем объединения частных тестов на основе шинной организации передачи данных между модулями.

Микропрограммный подход решает задачу следующим образом. Выбирается некоторая микропрограмма, состоящая из связанных микроопераций и осуществляющая передачу данных от внешних входов к внешним выходам устройства. Определяется часть аппаратуры, участвующая в реализации этой микропрограммы. Подбираются операнды, обнаруживающие неисправности этой части аппаратуры при выполнении каждой микрооперации. Решается задача оптимального выбора множества микропрограмм, покрывающего все аппаратные средства системы.

Функциональный подход основан на тестировании функций микропроцессорной системы. Список команд микропроцессора является источником информации о его операциях. Последние делятся на несколько классов: операции обработки; пересылки; ветвления: ввода-вывода и др. Тестируются каждая функция и та часть аппаратуры микропроцессора, которая реализует эту функцию («механизм» по терминологии). Выделяют следующие основные механизмы микропроцессора:

- механизмы обработки данных: выполнения арифметических и логических операций, модификации операндов и результата, формирования признаков результата, адресной арифметики;

- механизмы управления обработкой данных: дешифрации операций, дешифрации модификаций операций, операндов и результата, активизации операций и модификаций;

- механизмы хранения и передачи данных;

- механизмы управления передачей данных: выборки регистров, управления межрегистровым обменом, адресации, реакции на внутреннее состояние;

- механизмы реакции на внешние сигналы и сигналы ввода-вывода данных, прерывания, прямого доступа в память и др.

Основой построения моделей механизмов является модель регистровых передач. Тестовые программы строятся для каждого механизма в предположении, что остальные механизмы являются исправными.

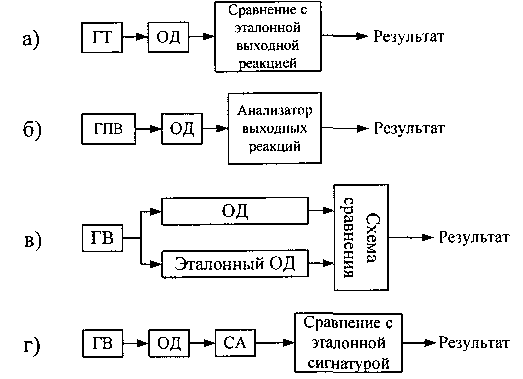

На рисунке 1 показаны основные схемы тестового диагностирования БИС.

Рисунок 1 - Основные схемы тестового диагностирования БИС

Схема программного тестирования (рисунок 1 а) содержит генератор тестов, которые хранятся в памяти и подаются на входы ОД в специально отведенные для этого интервалы времени. Выходная реакция сравнивается с эталонной, которая также хранится в памяти. При реализации программ тестирования применяются условные или безусловные алгоритмы диагностирования. Поиск дефектов осуществляется с помощью словарей или зондов.

При вероятностном тестировании (рисунок 1 б) входные воздействия на входы ОД подаются от генератора псевдослучайных воздействий, который строится на сдвиговом регистре с обратными связями. ОД осуществляет определенное преобразование распределения вероятностей этих сигналов. Анализатор выходных реакций проверяет соответствие параметров выходных случайных сигналов некоторым эталонным величинам. Устройство считается исправным, если статистически подтверждается такое соответствие. Вероятностное тестирование освобождает разработчика от сложного синтеза детерминированных тестов и, в то же время, обеспечивает достаточную достоверность результатов.

Компактное тестирование (рисунок 1 в) состоит в том, что ГВ подает воздействие одновременно на тестируемый ОД и на эталонный (дублирующий) ОД. Эти сигналы могут быть наборами детерминированного или псевдослучайного тестов. Результат диагностирования определяется из сравнения реакций обоих комплектов аппаратуры. Это исключает необходимость хранения или даже вычисления результатов тестирования.

При сигнатурном тестировании выходные реакции ОД обрабатываются сигнатурным анализатором. Полученные сигнатуры сравниваются с эталонными, которые могут быть получены расчётным путём или физическим моделированием. Данный метод позволяет значительно сократить объем хранимой информации.

Тестирование АЛУ.

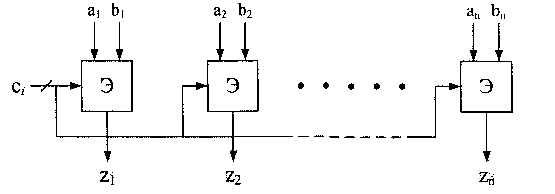

При проверке исправности АЛУ тестируются логические, арифметические и другие операции. Механизм выполнения одноместных и двухместных логических операций представляет собой регулярную структуру из п одинаковых элементов с одним или двумя входами. На рисунке 1 показана такая структура для двухместной операции. Элемент Э является многофункциональным и выполняет ту или иную операцию в зависимости от значения вектора настройки с i.

Рисунок 1 – Выполнение двухместной логической операции

Функции каждого разряда Z1, Z2 … Zn вычисляются независимо друг от друга. Поэтому для тестирования двухместной функции достаточно четырех наборов, которые образуют полный тест. Если АЛУ выполняет k двухместных функций, то тест содержит 4k набора. Такой тест обнаруживает все одиночные и кратные неисправности, при условии отсутствия ошибок в работе схемы дешифрации операций (сигнал c i является правильным).

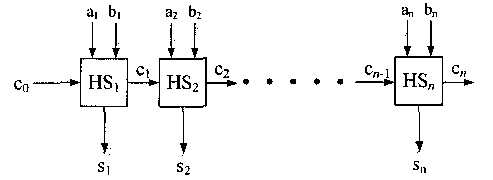

Основой выполнения арифметических операций является суммирование, которое реализуется сумматорами различных типов. На рисунке 2 показан сумматор с последовательным переносом.

Рисунок 2 - Сумматор с последовательным переносом

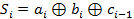

Он представляет собой регулярную структуру, состоящую из базовых модулей - одноразрядных сумматоров HS. На входы i -го модуля HS подаются значения i -ro разряда а i и b iоперандов слагаемых и сигнал переноса с i из предыдущего разряда. Значения выходов суммы и переноса определяются по формулам:  и

и

В таблице 1 приведен проверяющий тест структуры, изображенной на рисунке 2. Он содержит 8 для любого числа разрядов n и любой внутренней реализации модуля HS. Тест обнаруживает все одиночные неисправности сумматора.

Таблица 1

| № | с0 | a1b1 | a2b2 | a3b3 | |

| I | |||||

Тестирование ЗУ.

Правильная работа ЗУ является важным условием работоспособности микропроцессорных систем. Тестирование БИС ЗУ обычно проводится перед установкой ее в типовой элемент замены (ТЭЗ). При этом могут осуществляться статический, динамический и функциональный виды контроля. При статическом контроле измеряются электрические величины в установившемся режиме: токи логических «0» и «1» входных и выходных сигналов, ток потребления. При динамическом контроле проверяются временные параметры микросхемы (время выбора микросхемы, время выборки адреса, время выборки считывания и др.). Целью функционального контроля является проверка правильности работы узлов БИС ОЗУ с учетом их электрических связей во всех режимах работы (записи, считывания, регенерации информации) при различных кодах адреса и входной информации. Функциональные тесты различаются своей длительностью и обнаруживающей способностью. Используются тесты типов L, L 2и L 2/3, где L – емкость микросхемы памяти. Анализ выходных реакций на тесте осуществляется путём сравнения с эталонными реакциями. При этом возможно сжатие диагностической информации, например с помощью сигнатурных анализаторов.

Далее приведены некоторые из наиболее распространённых функциональных тестов и их свойства.

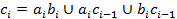

1. «Последовательная запись и считывание нулей и единиц». Производится запись нулей (единиц) во все ячейки ОЗУ, после чего производятся последовательное считывание и проверка этой информации (рисунок 3а).

2. «Шахматный код». В соседние биты матрицы ЗУ записывается взаимноинверсная информация. Затем содержимое всех ячеек последовательно считывается. Тест обнаруживает взаимовлияния между соседними элементами памяти (рисунок 3б).

3. «Запись-считывание в прямом и обратном направлении». Во все ячейки ОЗУ записываются нули. Затем производятся последовательное считывание содержимого каждой ячейки и запись в неё единиц. После записи единиц в последнюю ячейку процедура повторяется от старшего адреса к младшему с чтением единиц и записью нулей. Тест обнаруживает взаимовлияния соседних ячеек при смене в них информации.

4. «Чётность-нечётность адреса». В каждую ячейку записывается 0, если число единиц в адресном коде четно, и 1, если число единиц нечетно. Затем производится считывание по всем адресам. Эта процедура повторяется с контролем нечётности.

5. «Бегущая 1 или 0». В первую ячейку ОЗУ записываются 1 (0), а во все остальные - фоновые 0 (1). Затем все адреса последовательно считываются с проверкой. Последней считывается первая ячейка с последующей записью в неё 0(1). Процедура повторяется для второй ячейки и всех последующих (рисунок 3г). Тест обнаруживает сбои и отказы, возникающие при переходе элементов памяти из 1 в 0, и наоборот, а также обнаруживает влияние операции записи в отдельную ячейку на сохранность информации в ОЗУ.

6. «Попарное считывание». Тест проверяет любые адресные переходы со всевозможным изменением информации при считывании. В первую ячейку ОЗУ А0 записываются 1, а в остальные - нули. Затем последовательно считываются с проверкой адреса А1, А0; затем А2, А0 и т.д., пока все пары переходов, включающие А0, не будут проверены. Подобная процедура повторяется для ячейки А1 и т.д. Цикл повторяется для инверсной информации. С помощью данного теста проверяется функционирование накопительной части ОЗУ, дешифратора, а также влияние записи на сохранность информации.

7. «Бегущий столбец». В первый столбец матрицы ОЗУ записывается 1 на фоне остальных 0. Затем вся информация считывается с последующей записью 0 в первый столбец. Процедура повторяется для второго столбца и т.д. до последнего (рисунок 3д).

8. «Бегущая строка». В первую строку записывается 1 на фоне остальных 0. Затем вся информация считывается с последующей записью 0 в первую строку. Процедура повторяется для каждой строки и т.д. до последней (рисунок 3е).

Рисунок 3 - Алгоритмы формирования тестов для ОЗУ

43. Тестирование программ.

Микропроцессорная система есть единство аппаратных и программных средств. Поэтому тестирование программ является второй важнейшей задачей наряду с тестированием аппаратуры. С точки зрения диагностирования, программное обеспечение представляет собой объект более сложный, чем аппаратные средства. Этому есть несколько причин. Во-первых, программные продукты менее структурированы, чем аппаратура. Последняя часто строится на стандартных блоках, тесты для которых известны или легко строятся. Сложность программы может достигать десятков тысяч операторов, что делает их обозримыми. Воздействия программных ошибок гораздо более обширны по своим последствиям на вычислительные процессы, чем воздействия, вызванные неисправностями аппаратных средств.

Любое тестирование и отладка сложных систем ПО могут только показать наличие ошибок, но не доказать их отсутствие. Поэтому программисты говорят: «Последняя найденная в программе ошибка является на самом деле предпоследней». В то же время последствия ошибок ПО могут быть весьма серьезными. Стал уже классическим пример, когда из-за одной ошибки в операторе на Фортране не состоялся запуск американского космического корабля на Венеру. Особенно важно отсутствие ошибок ПО в безопасных системах. Например, в микропроцессорных централизациях стрелок и сигналов на станциях программным путем проверяются условия безопасности при установке маршрутов и открытии сигналов (свободность участков маршрута, контроль положения стрелок, отсутствие враждебных маршрутов и другие).

Ошибки ПО можно разделить на программные, алгоритмические и системные. Программные ошибки вызываются неправильной записью команд на языке программирования и ошибками при трансляции. Их количество зависит от квалификации программистов, степени автоматизации программирования, глубины и качества тестирования. Алгоритмические ошибки возникают из-за некорректной формулировки алгоритма ее решения. Типичные причины возникновения таких ошибок состоят в неполном учете условий решения, диапазонов изменения переменных, в превышении выделенных ресурсов, в неправильной оценке времени реализации отдельных программных модулей и т.п. Обнаружить алгоритмические ошибки сложнее, чем программные. Еще труднее обнаруживаются системные ошибки, которые связаны с неправильным взаимодействием комплексов программ между собой и с внешними объектами.

Статистика показывает, что интенсивность ошибок в ПО лежит в диапазоне от 0,25 до 10 на 1000 команд. Исправление одной программной, алгоритмической или системной ошибки требует корректировки в среднем 6, 14 или 25 команд соответственно. При этом материальные затраты на исправление ошибки с течением времени жизненного никла ПО возрастают, а вероятность правильного исправления ошибки уменьшается. Поэтому целесообразно осуществлять тестирование ПО с самого начала его разработки, учитывая то, что на тестирование и сопровождение (устранение ошибок в процессе эксплуатации) приходится до 75% всех материальных затрат. По мере исправления ошибок в процессе сопровождения (если при этом не вносятся новые ошибки) частота отказов в ПО уменьшается (рисунок 1), поскольку программы «не изнашиваются» и «не стареют» в отличие от аппаратуры.

Рисунок 1 – Зависимость частоты отказов аппаратуры (1) и ПО (2) от времени

Эффективное тестирование ПО возможно только в том случае, если при его построении используются принципы структурного программирования. В этом случае программа делится на отдельные программные модули, которые решают определенные функционально законченные задачи, имеют небольшую сложность и поэтому могут быть сравнительно легко протестированы. Модули должны быть максимально независимы друг от друга. Программа имеет иерархическую структуру, в которой модули верхних уровней управляют работой модулей нижних уровней. Связи между модулями должны быть минимальны и по возможности сводиться только к передаче данных.

Тестирование состоит в выполнении программы с целью обнаружения ошибок при отсутствии реальной внешней среды. Специально подбирают входные данные (тесты); реакция ПО для данных сравнивается с эталонной. В структурированной программе выделяют четыре уровня тестирования: тестирование модулей, сопряжений между модулями, тестирование внешних функций, комплексное тестирование.

На уровне модулей проверяют логику программы. Контроль сопряжений обнаруживает ошибки в межмодульном интерфейсе. Тестирование внешних функций определяет соответствие внешних спецификаций и функций программы. Комплексное тестирование является завершающим этапом проверки системы.

Тестирование разделяется на три этапа: составление (генерация) тестов, выполнение программы на этих тестах и оценку полученных результатов. Выполнение программы на тестах может осуществляться вручную (на бумаге, «в уме») для несложных программ. Такой вид тестирования называется статическим(в ручную). Динамическое тестирование выполняется с использованием ЭВМ. Результаты прохождения анализирует программист или ЭВМ, для чего требуется иметь эталонные результаты и хранить их в памяти для сравнения. Возможно также использование эталонной программы, которая запускается на тех же тестах и вырабатывает эталонные выходные данные.

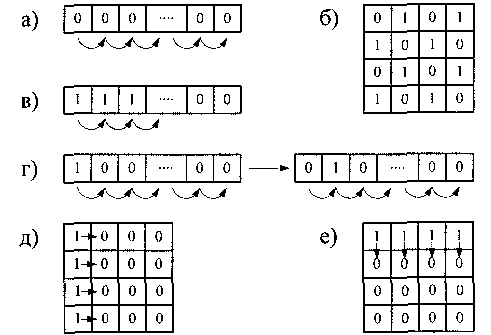

Тесты составляют программисты или автоматические системы генерации тестов. При этом используются два подхода: функциональный и структурный (рисунок 2).

Рисунок 2 – Методы тестирования программ

Рассмотрим эти подходы на примере тестов для бинарной программы вычисления булевой функции

Метод бинарных программ основан на том, что процесс вычисления булевой функции можно свести к последовательности выполнения команд условного перехода i: если А, то j, иначе i+ 1, где i – порядковый номер команды: А – булева переменная, значение которой проверяется данной командой. Если А = 1, то осуществляется переход к выполнению команды с порядковым номером j, если А = 0 – переход к выполнению команды с порядковым номером i +1.

44. Средства функционального диагностирования МПС

Области применения тестового диагностирования – производство, отладка и ремонт микропроцессорных систем. В процессе работы системы, для обнаружения ошибок используются средства функционального контроля. В этом случае тестовыми воздействиями являются рабочие входные воздействия, а ошибки обнаруживаются практически немедленно. Однако полнота контроля в целом меньше, чем при тестировании. Эффективным является одновременное применение обоих видов контроля, когда периодически через некоторое время tД выделяется интервал времени τД для тестового диагностирования.

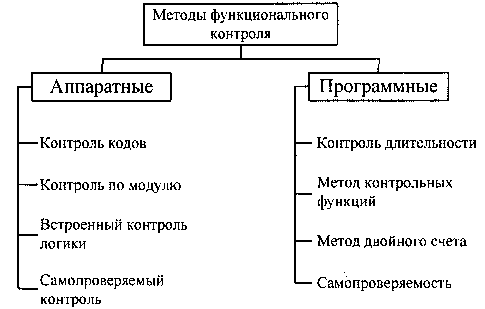

В микропроцессорной системе выполняются три основных вида операций, которые надо контролировать: передача информации, логические и арифметические операции. Для их контроля используются аппаратные и программные методы (рисунок 1). Аппаратный контроль имеет высокое быстродействие, но требует дополнительных затрат аппаратуры. Программный контроль не связан с аппаратной избыточностью, но использует дополнительное процессорное время для выполнения программ контроля. В большинстве сложных микропроцессорных систем сочетаются аппаратные и программные средства контроля.

Рисунок 1 -Методы функционального контроля МПС

При передаче информации для ее контроля используются избыточные коды с обнаружением и исправлением ошибок. Код называется избыточным, если для передачи информации используют не все возможные кодовые слова. В этом случае для n-разрядно кода выполняется неравенство N < 2 n, где N – число используемых кодовых слов (ёмкость кода). Кодовым расстоянием d называется минимальное число разрядов, которыми различаются два кодовых слова. Код с кодовым расстоянием d обнаруживает ошибки в t разрядах и менее, если выполняется неравенство d ≥ t + 1 и исправляет ошибки в r разрядах и менее, если d ≥ 2 r + 1.

Коды с обнаружением ошибок применяются при передаче данных в шинах микропроцессорных систем и при хранении и передаче данных в регистрах. Наиболее часто используется для этих целей код с контролем на чётность, который образуется добавлением одного избыточного (контрольного) разряда. Кодовое расстояние этого кода равно 2, что обеспечивает обнаружение всех одиночных ошибок и любого нечётного числа ошибок.

Коды с исправлением ошибок используются в оперативной памяти, в запоминающих устройствах на магнитных лентах и дисках. Наиболее распространён код Хемминга, который обнаруживает одиночные и исправляет двойные ошибки.

Для контроля арифметических операций в цифровых ЭВМ широко используется контроль по модулю. В этом случае каждому числу А, участвующему в арифметической операции, сопоставляется остаток по модулю R, определяемый из равенства A = aQ + R, где Q – модуль; а – целая часть отношения A/Q. Смысл применения контроля по модулю заключается в том, что разрядность остатка R(A) существенно меньше разрядности числа А. Поэтому затраты аппаратуры для контрольных вычислений также существенно меньше.

Логические преобразования в вычислительных системах контролируют схемы встроенного контроля (СВК). Общая структура контроля с использованием СВК приведена на рисунке 2.

Рисунок 2 – Структура контроля с помощью СВК

Поиск по сайту: